CHAPTER 2 NDA-24296

Page 44

Revision 1.0

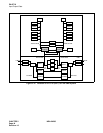

PH-GT10

Input Output Gate

Figure 2-12 Location of PH-GT10 (IOGT) for IPX-UMG System

HSW01

HSW00

TSW03

TSW02

TSW01

TSW00

LANI

LANI

P-BUS

LANI

LANI

P-BUS

HSW11

HSW10

TSW13

TSW12

TSW11

TSW10

PLO 1

PLO 0

RES

CPU CPU

MMC

MISC

EMA

RES

RES RES

(IOGT1)

PH-GT10

(IOGT0)

PH-GT10

ISAGT

ISAGT

ISAGT2

ISAGT2

PCI MEM

PCI BUS PCI BUS

PCI MEM

MISC

I/O

BUS

MISC

I/O

BUS

ISAGT BUSISAGT BUS

CMP

TSW I/O BUSTSW I/O BUS

ISWM