www.ti.com

PRODUCT PREVIEW

7.6ResetController

7.6.1Power-onReset(PORPin)

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

TheresetcontrollerdetectsthedifferenttypeofresetssupportedontheC6454deviceandmanagesthe

distributionofthoseresetsthroughoutthedevice.

TheC6454devicehasseveraltypesofresets:power-onreset,warmreset,systemreset,andCPUreset.

Table7-12explainsfurtherthetypesofreset,theresetinitiator,andtheeffectsofeachresetonthechip.

FormoreinformationontheeffectsofeachresetonthePLLcontrollersandtheirclocks,see

Section7.6.7,ResetElectricalData/Timing.

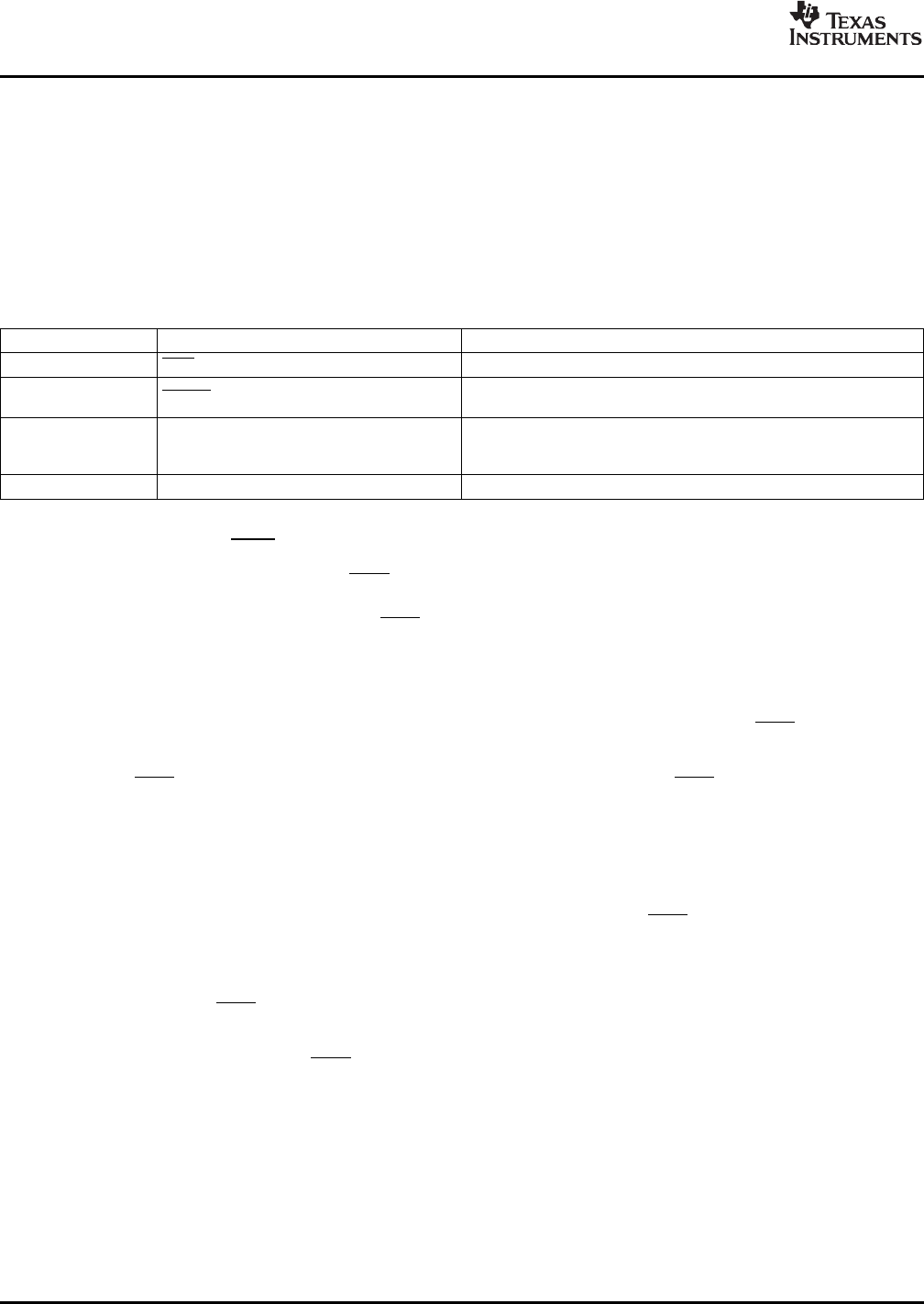

Table7-12.ResetTypes

TYPEINITIATOREFFECT(s)

Power-onResetPORpinResetstheentirechipincludingthetestandemulationlogic.

ResetseverythingexceptforthetestandemulationlogicandPLL2.

WarmResetRESETpin

EmulatorstaysaliveduringWarmReset.

Asystemresetmaintainsmemorycontentsanddoesnotresetthe

SystemResetEmulatortestandemulationcircuitry.Thedeviceconfigurationpinsarealso

notre-latchedandthestateoftheperipheralsisalsonotaffected.

(1)

CPULocalResetHPI/PCICPUlocalreset.

(1)OntheC6454device,peripheralscanbeinoneofseveralstates.ThesestatesarelistedinTable3-4.

Power-onResetisinitiatedbythePORpinandisusedtoresettheentirechip,includingthetestand

emulationlogic.Power-onResetisalsoreferredtoasacoldresetsincethedeviceusuallygoesthrougha

power-upcycle.Duringpower-up,thePORpinmustbeasserted(drivenlow)untilthepowersupplies

havereachedtheirnormaloperatingconditions.Notethatadevicepower-upcycleisnotrequiredto

initiateaPower-onReset.

ThefollowingsequencemustbefollowedduringaPower-onReset:

1.WaitforallpowersuppliestoreachnormaloperatingconditionswhilekeepingthePORpinasserted

(drivenlow).

WhilePORisasserted,allpinswillbesettohigh-impedance.AfterthePORpinisdeasserted(driven

high),allZgrouppins,lowgrouppins,andhighgrouppinsaresettotheirresetstateandwillremain

attheirresetstateuntiltheotherwiseconfiguredbytheirrespectiveperipheral.Allperipherals,except

thoseselectedforbootpurposes,aredisabledafteraPower-onResetandmustbeenabledthrough

theDeviceStateControlregisters;formoredetails,seeSection3.3,PeripheralSelectionAfterDevice

Reset.

2.Onceallthepowersuppliesarewithinvalidoperatingconditions,thePORpinmustremainasserted

(low)foraminimumof256CLKIN2cycles.ThePLL1controllerinputclock,CLKIN1,andthePCIinput

clock,PCLK,mustalsobevalidduringthistime.PCLKisonlyneededifthePCImoduleisbeingused.

IftheDDR2memorycontrollerandtheEMACperipheralarenotneeded,CLKIN2canbetiedlowand,

inthiscase,thePORpinmustremainasserted(low)foraminimumof256CLKIN1cyclesafterall

powersupplieshavereachedvalidoperatingconditions.

WithinthelowperiodofthePORpin,thefollowinghappens:

–Theresetsignalsflowtotheentirechip(includingthetestandemulationlogic),resettingmodules

thatuseresetasynchronously.

–ThePLL1controllerclocksarestartedatthefrequencyofthesystemreferenceclock.Theclocks

arepropagatedthroughoutthechiptoresetmodulesthatuseresetsynchronously.Bydefault,

PLL1isinresetandunlocked.

–ThePLL2controllerclocksarestartedatthefrequencyofthesystemreferenceclock.PLL2isheld

inreset.SincethePLL2controlleralwaysoperatesinPLLmode,thesystemreferenceclockand

C64x+PeripheralInformationandElectricalSpecifications 116SubmitDocumentationFeedback