www.ti.com

PRODUCT PREVIEW

7.12.3HPIElectricalData/Timing

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

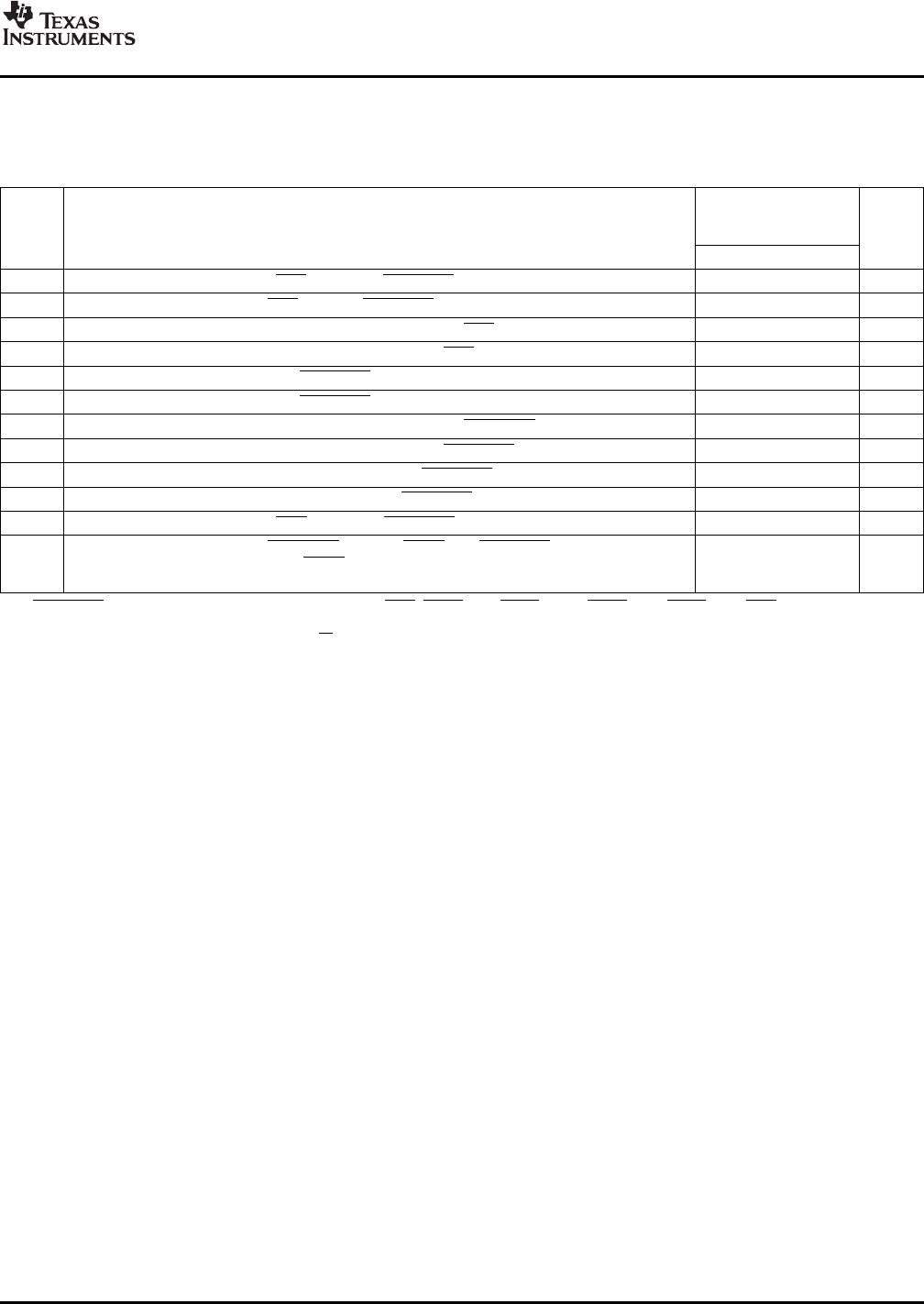

Table7-55.TimingRequirementsforHost-PortInterfaceCycles

(1)(2)

(seeTable7-56throughFigure7-51)

-720

-850

NO.UNIT

-1000

MINMAX

9t

su(HASL-HSTBL)

Setuptime,HASlowbeforeHSTROBElow5ns

10t

h(HSTBL-HASL)

Holdtime,HASlowafterHSTROBElow2ns

11t

su(SELV-HASL)

Setuptime,selectsignals

(3)

validbeforeHASlow5ns

12t

h(HASL-SELV)

Holdtime,selectsignals

(3)

validafterHASlow5ns

13t

w(HSTBL)

Pulseduration,HSTROBElow15ns

14t

w(HSTBH)

Pulseduration,HSTROBEhighbetweenconsecutiveaccesses2Mns

15t

su(SELV-HSTBL)

Setuptime,selectsignals

(3)

validbeforeHSTROBElow5ns

16t

h(HSTBL-SELV)

Holdtime,selectsignals

(3)

validafterHSTROBElow5ns

17t

su(HDV-HSTBH)

Setuptime,hostdatavalidbeforeHSTROBEhigh5ns

18t

h(HSTBH-HDV)

Holdtime,hostdatavalidafterHSTROBEhigh1ns

37t

su(HCSL-HSTBL)

Setuptime,HCSlowbeforeHSTROBElow0ns

Holdtime,HSTROBElowafterHRDYlow.HSTROBEshouldnotbe

38t

h(HRDYL-HSTBL)

inactivateduntilHRDYisactive(low);otherwise,HPIwriteswillnot1.1ns

completeproperly.

(1)HSTROBEreferstothefollowinglogicaloperationonHCS,HDS1,andHDS2:[NOT(HDS1XORHDS2)]ORHCS.

(2)M=SYSCLK3period=6/CPUclockfrequencyinns.Forexample,whenrunningpartsat1000MHz,useM=6ns.

(3)Selectsignalsinclude:HCNTL[1:0]andHR/W.ForHPI16modeonly,selectsignalsalsoincludeHHWIL.

SubmitDocumentationFeedbackC64x+PeripheralInformationandElectricalSpecifications167