www.ti.com

PRODUCT PREVIEW

4

5

1

2

AECLKIN

AECLKOUT1

3 3

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

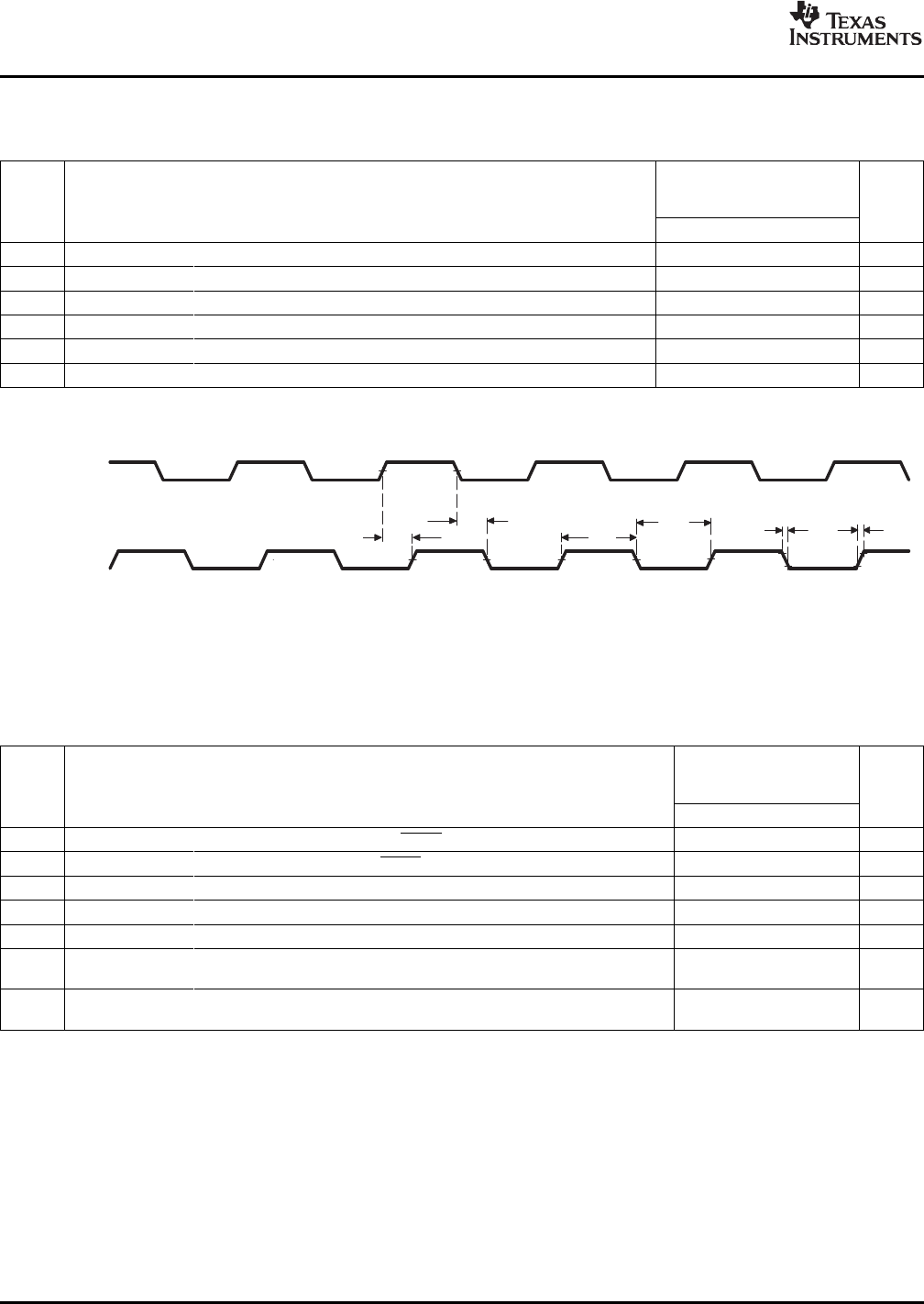

Table7-43.SwitchingCharacteristicsOverRecommendedOperatingConditionsforAECLKOUTforthe

EMIFAModule

(1)(2)(3)

(seeFigure7-32)

-720

-850

NO.PARAMETERUNIT

-1000

MINMAX

1t

c(EKO)

Cycletime,AECLKOUTE–0.7E+0.7ns

2t

w(EKOH)

Pulseduration,AECLKOUThighEH–0.7EH+0.7ns

3t

w(EKOL)

Pulseduration,AECLKOUTlowEL–0.7EL+0.7ns

4t

t(EKO)

Transitiontime,AECLKOUT1ns

5t

d(EKIH-EKOH)

Delaytime,AECLKINhightoAECLKOUThigh18ns

6t

d(EKIL-EKOL)

Delaytime,AECLKINlowtoAECLKOUTlow18ns

(1)E=theEMIFinputclock(AECLKINorSYSCLK4)periodinnsforEMIFA.

(2)ThereferencepointsfortheriseandfalltransitionsaremeasuredatV

OL

MAXandV

OH

MIN.

(3)EHisthehighperiodofE(EMIFinputclockperiod)innsandEListhelowperiodofE(EMIFinputclockperiod)innsforEMIFA.

Figure7-32.AECLKOUTTimingfortheEMIFAModule

7.10.3.1AsynchronousMemoryTiming

Table7-44.TimingRequirementsforAsynchronousMemoryCyclesforEMIFAModule

(1)(2)(3)

(seeFigure7-33andFigure7-34)

-720

-850

NO.UNIT

-1000

MINMAX

3t

su(EDV-AOEH)

Setuptime,AEDxvalidbeforeAAOEhigh6.5ns

4t

h(AOEH-EDV)

Holdtime,AEDxvalidafterAAOEhigh3ns

5t

su(ARDY-EKOH)

Setuptime,AARDYvalidbeforeAECLKOUTlow1ns

6t

h(EKOH-ARDY)

Holdtime,AARDYvalidafterAECLKOUTlow2ns

7t

w(ARDY)

Pulsewidth,AARDYassertionanddeassertion2E+5ns

Delaytime,fromAARDYsampleddeassertedonAECLKOUTfallingto

8t

d(ARDY-HOLD)

4Ens

beginningofprogrammedholdperiod

Setuptime,beforeendofprogrammedstrobeperiodbywhichAARDY

9t

su(ARDY-HOLD)

2Ens

shouldbeassertedinordertoinsertextendedstrobewaitstates.

(1)E=AECLKOUTperiodinnsforEMIFA

(2)Toensuredatasetuptime,simplyprogramthestrobewidthwideenough.

(3)AARDYisinternallysynchronized.TouseAARDYasanasynchronousinput,thepulsewidthoftheAARDYsignalshouldbeatleast2E

toensuresetupandholdtimeismet.

C64x+PeripheralInformationandElectricalSpecifications 152SubmitDocumentationFeedback