www.ti.com

PRODUCT PREVIEW

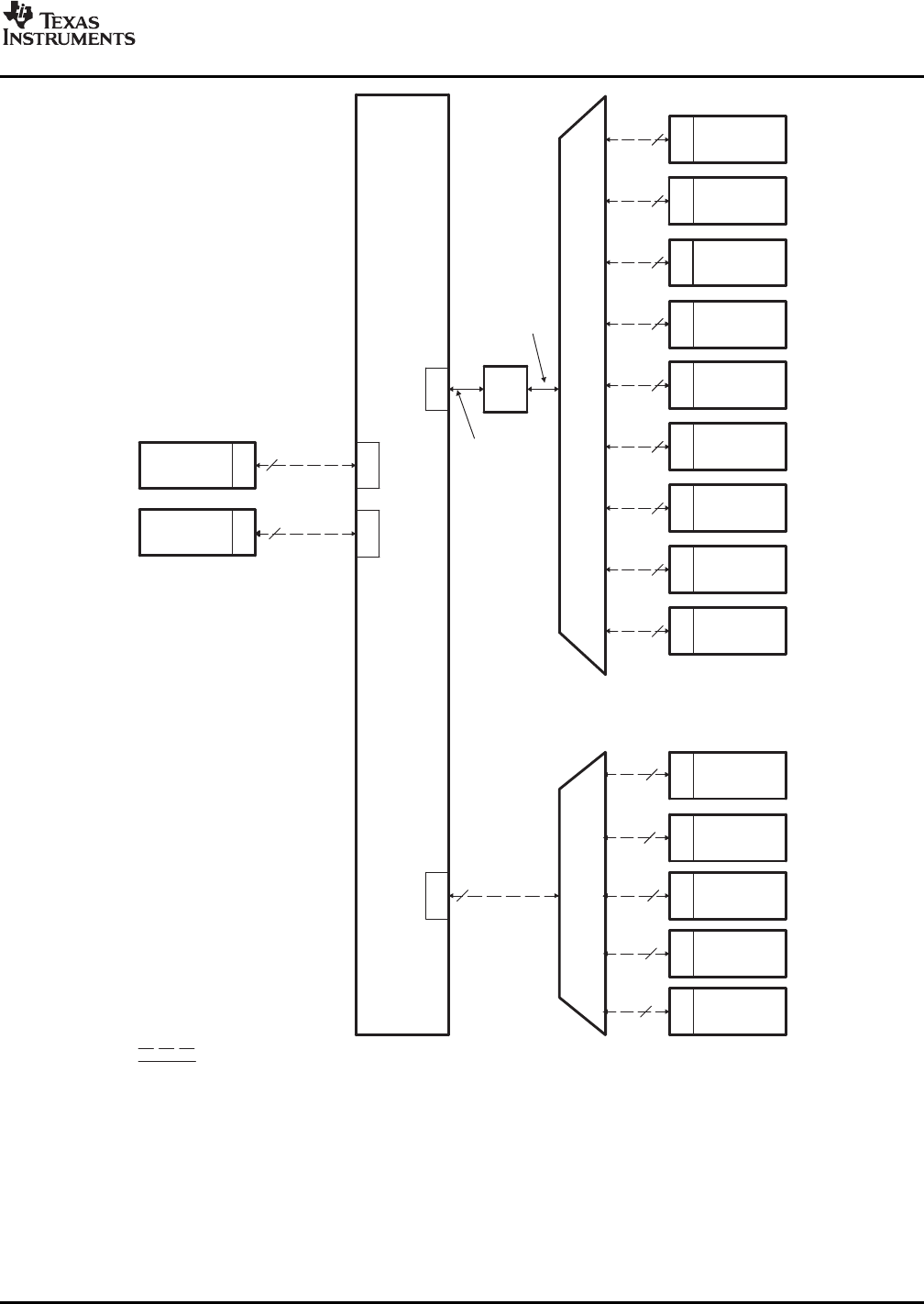

Megamodule

M

CFG SCR

S

M

McBSPs

S

Timers

S

HPI

S

PCI

S

S

Bridge

7

GPIO

S

EMAC/MDIO

M

Data SCR

S

S

I2C

SS

PLL

Controllers

(A)

S

S

Device

Configuration

Registers

(A)

EDMA3 TC0

S

EDMA3 TC1

S

S EDMA3 TC2

S

EDMA3 CC

SS

EDMA3 TC3

S

M

32

(SYSCLK3)

MUX

32

(SYSCLK2)

32

(SYSCLK2)

32 (SYSCLK2)

32

(SYSCLK3)

32 (SYSCLK2)

32 (SYSCLK2)

32-bit

(SYSCLK2)

Configuration Bus

Data Bus

MUX

32

(SYSCLK2)

32

(SYSCLK2)

32

(SYSCLK2)

32

(SYSCLK2)

A. Only accessible by the C64x+ Megamodule.

B. All clocks in this figure are generated by the PLL1 controller.

32

(SYSCLK3)

32

(SYSCLK3)

32

(SYSCLK3)

32

(SYSCLK3)

32

(SYSCLK3)

32

(SYSCLK3)

32

(SYSCLK3)

32

(SYSCLK3)

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

Figure4-2.C64x+Megamodule-SCRConnection

SubmitDocumentationFeedbackSystemInterconnect75