www.ti.com

PRODUCT PREVIEW

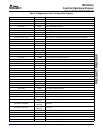

4K bytes

8K bytes

16K bytes

L1P memory

00E0 0000h

00E0 4000h

00E0 6000h

00E0 7000h

00E0 8000h

direct

mapped

SRAM

1/2

dm

3/4

SRAM

SRAM

7/8

All

SRAM

000 001 010 011 100

Block base

address

L1P mode bits

cache

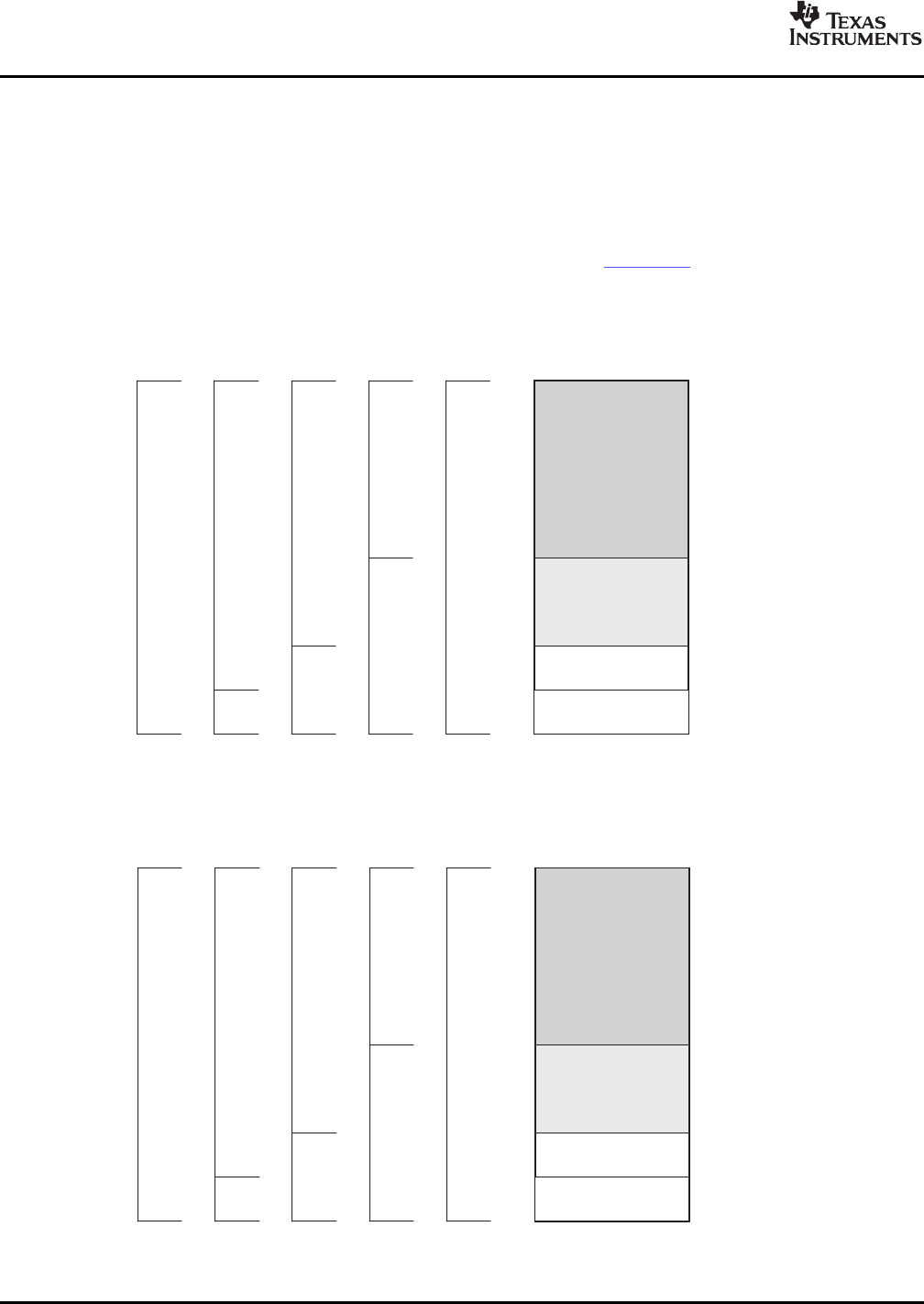

4K bytes

cache

direct

mapped

cache

direct

mapped

cache

4K bytes

8K bytes

16K bytes

L1D memory

00F0 0000h

00F0 4000h

00F0 6000h

00F0 7000h

00F0 8000h

2-way

SRAM

1/2

2-way

3/4

SRAM

SRAM

7/8

All

SRAM

000 001 010 011 100

Block base

address

L1D mode bits

cache

4K bytes

cache

2-way

cache

2-way

cache

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

•Region1sizeis32Kbyteswithnowaitstates.

L1Disatwo-wayset-associativecachewhileL1Pisadirect-mappedcache.

TheL1PandL1DcachecanbereconfiguredviasoftwarethroughtheL1PMODEfieldoftheL1P

ConfigurationRegister(L1PMODE)andtheL1DMODEfieldoftheL1DConfigurationRegister(L1DCFG)

oftheC64x+Megamodule.Afterdevicereset,L1PandL1Dcacheareconfiguredasallcacheorall

SRAM.Theon-chipBootloaderchangestheresetconfigurationforL1PandL1D.Formoreinformation,

seetheTMS320C645xBootloaderUser'sGuide(literaturenumberSPRUEC6).

Figure5-2andFigure5-3showtheavailableSRAM/cacheconfigurationsforL1PandL1D,respectively.

Figure5-2.TMS320C6454L1PMemoryConfigurations

Figure5-3.TMS320C6454L1DMemoryConfigurations

C64x+Megamodule 78SubmitDocumentationFeedback