www.ti.com

PRODUCT PREVIEW

5.2MemoryProtection

5.3BandwidthManagement

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

MemoryprotectionallowsanoperatingsystemtodefinewhoorwhatisauthorizedtoaccessL1D,L1P,

andL2memory.Toaccomplishthis,theL1D,L1P,andL2memoriesaredividedintopages.Thereare16

pagesofL1P(2KBeach),16pagesofL1D(2KBeach),and16pagesofL2(64KBeach).TheL1D,L1P,

andL2memorycontrollersintheC64x+Megamoduleareequippedwithasetofregistersthatspecifythe

permissionsforeachmemorypage.

Eachpagemaybeassignedwithfullyorthogonaluserandsupervisorread,write,andexecute

permissions.Additionally,apagemaybemarkedaseither(orboth)locallyorgloballyaccessible.Alocal

accessisadirectCPUaccesstoL1D,L1P,andL2,whileaglobalaccessisinitiatedbyaDMA(either

IDMAortheEDMA3)orbyothersystemmasters.NotethatEDMAorIDMAtransfersprogrammedbythe

CPUcountasglobalaccesses.

TheCPUandthesystemmastersontheC6454deviceareallassignedaprivilegeIDof0.Thereforeitis

onlypossibletospecifywhethermemorypagesarelocallyorgloballyaccessible.TheAID0andLOCAL

bitsofthememoryprotectionpageattributeregistersspecifythememorypageprotectionscheme,see

Table5-1.

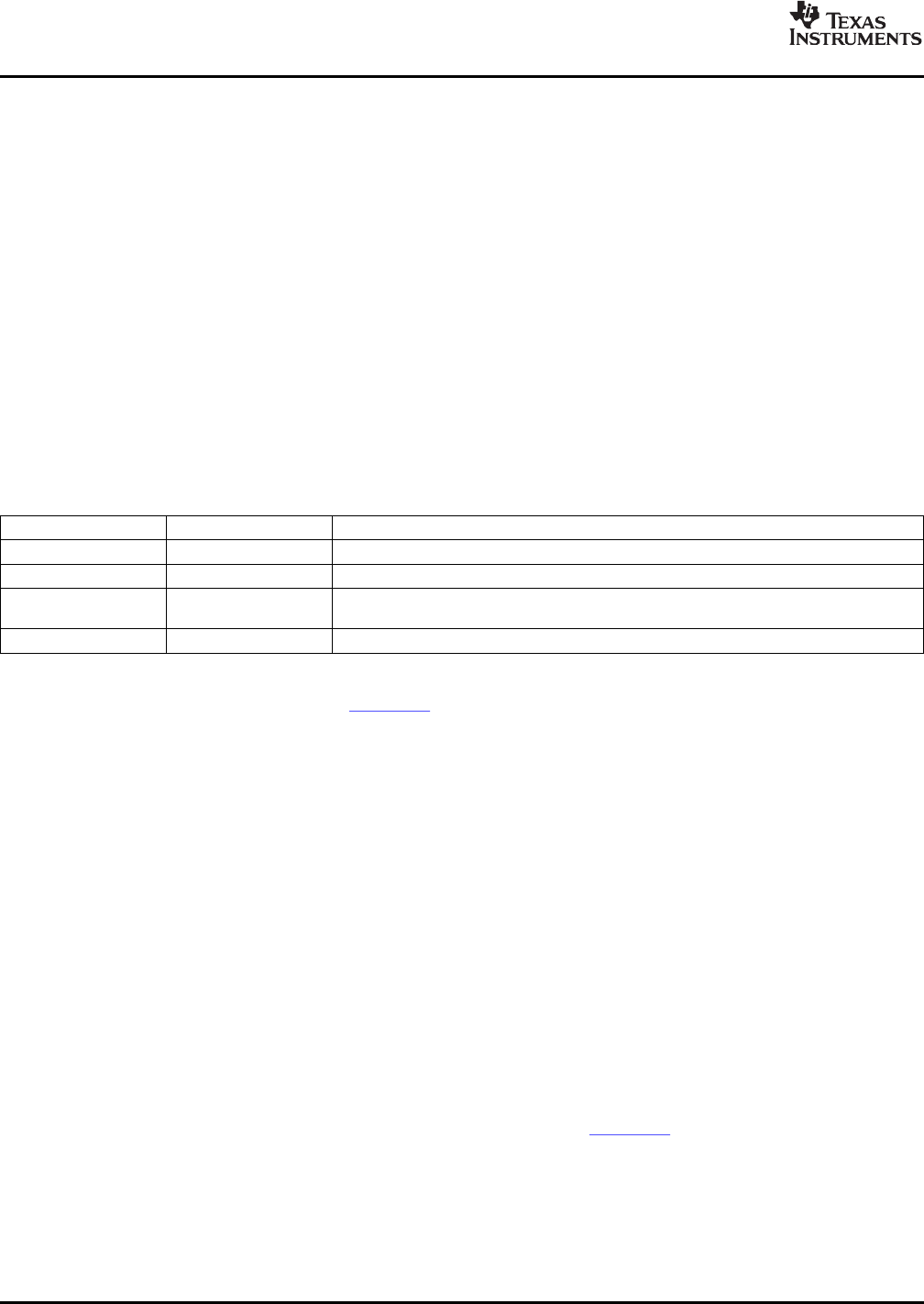

Table5-1.AvailableMemoryPageProtectionSchemes

AID0BitLOCALBitDescription

00Noaccesstomemorypageispermitted.

01OnlydirectaccessbyCPUispermitted.

10OnlyaccessesbysystemmastersandIDMAarepermitted(includesEDMAandIDMA

accessesinitiatedbytheCPU).

11Allaccessespermitted

FormoreinformationonmemoryprotectionforL1D,L1P,andL2,seetheTMS320C64x+Megamodule

ReferenceGuide(literaturenumberSPRU871).

WhenmultiplerequestorscontendforasingleC64x+Megamoduleresource,theconflictissolvedby

grantingaccesstothehighestpriorityrequestor.Thefollowingfourresourcesaremanagedbythe

BandwidthManagementcontrolhardware:

•Level1Program(L1P)SRAM/Cache

•Level1Data(L1D)SRAM/Cache

•Level2(L2)SRAM/Cache

•Memory-mappedregistersconfigurationbus

TheprioritylevelforoperationsinitiatedwithintheC64x+Megamodule;e.g.,CPU-initiatedtransfers,

user-programmedcachecoherencyoperations,andIDMA-initiatedtransfers,aredeclaredthrough

registersintheC64x+Megamodule.TheprioritylevelforoperationsinitiatedoutsidetheC64x+

MegamodulebysystemperipheralsisdeclaredthroughthePriorityAllocationRegister(PRI_ALLOC),see

Section4.4.SystemperipheralswithnofieldsinPRI_ALLOChavetheirownregisterstoprogramtheir

priorities.

MoreinformationonthebandwidthmanagementfeaturesoftheC64x+Megamodulecanbefoundinthe

TMS320C64x+MegamoduleReferenceGuide(literaturenumberSPRU871).

C64x+Megamodule 80SubmitDocumentationFeedback