www.ti.com

PRODUCT PREVIEW

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

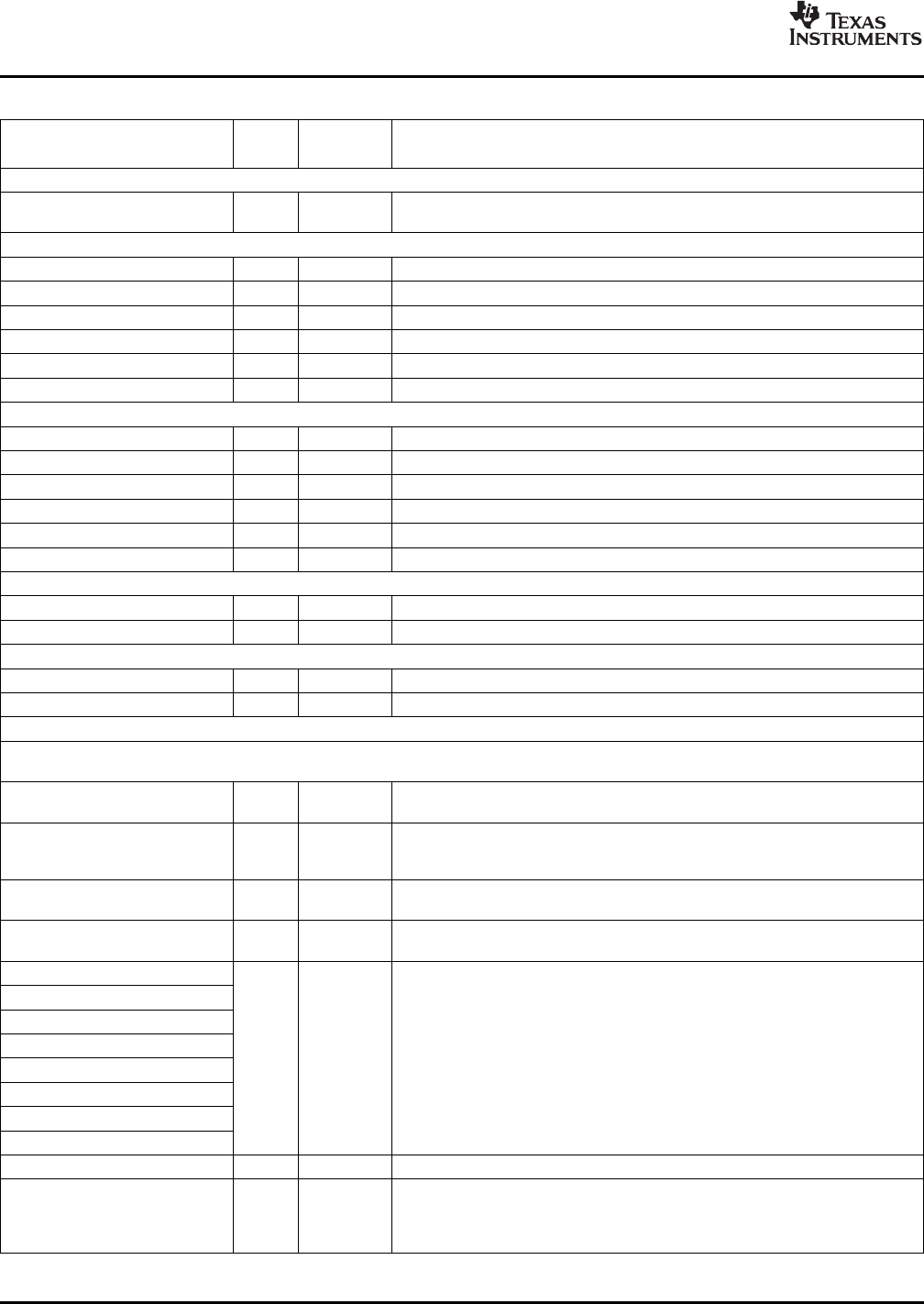

Table2-3.TerminalFunctions(continued)

SIGNAL

TYPE

(1)

IPD/IPU

(2)

DESCRIPTION

NAMENO.

MULTICHANNELBUFFEREDSERIALPORT1ANDMULTICHANNELBUFFEREDSERIALPORT0(McBSP1andMcBSP0)

McBSPexternalclocksource(asopposedtointernal)(I)

CLKSAJ4IIPD

[sharedbyMcBSP1andMcBSP0]

MULTICHANNELBUFFEREDSERIALPORT1(McBSP1)

CLKR1/GP[0]AF4I/O/ZIPDMcBSP1receiveclock(I/O/Z)orGP[0](I/O/Z)[default]

FSR1/GP[10]AE5I/O/ZIPDMcBSP1receiveframesync(I/O/Z)orGP[10](I/O/Z)[default]

DR1/GP[8]AH5I/O/ZIPDMcBSP1receivedata(I)orGP[8](I/O/Z)[default]

DX1/GP[9]AG5I/O/ZIPDMcBSP1transmitdata(O/Z)orGP[9](I/O/Z)[default]

FSX1/GP[11]AG4I/O/ZIPDMcBSP1transmitframesync(I/O/Z)orGP[11](I/O/Z)[default]

CLKX1/GP[3]AF5I/O/ZIPDMcBSP1transmitclock(I/O/Z)orGP[3](I/O/Z)[default]

MULTICHANNELBUFFEREDSERIALPORT0(McBSP0)

CLKR0AG1I/O/ZIPUMcBSP0receiveclock(I/O/Z)

FSR0AH3I/O/ZIPDMcBSP0receiveframesync(I/O/Z)

DR0AJ5IIPDMcBSP0receivedata(I)

DX0AF6I/O/ZIPDMcBSP0transmitdata(O/Z)

FSX0AJ3I/O/ZIPDMcBSP0transmitframesync(I/O/Z)

CLKX0AG6I/O/ZIPUMcBSP0transmitclock(I/O/Z)

MANAGEMENTDATAINPUT/OUTPUT(MDIO)FORMII/RMII/GMII

MDCLKM5I/O/ZIPDMDIOserialclock(MDCLK)forMII/RMII/RGMIImode(O)

MDION3I/O/ZIPUMDIOserialdata(MDIO)forMII/RMII/RGMIImode(I/O)

MANAGEMENTDATAINPUT/OUTPUT(MDIO)FORRGMII

RGMDCLKB4O/ZMDIOserialclockforRGMIImode(RGMDCLK)(O)

RGMDIOA4I/O/ZMDIOserialdataforRGMIImode(RGMDIO)(I/O)

ETHERNETMAC(EMAC)[MII/RMII/GMII]

Therearetwoconfigurationpins—theMAC_SEL[1:0](AEA[10:9]pins)thatselectoneofthefourinterfacemodes(MII,RMII,GMII,or

RGMII)fortheEMAC/MDIOinterface.FormoredetailedinformationontheEMACconfigurationpins,seeSection3,DeviceConfiguration.

ThispinisEMACreceiveclock(MRCLK)forMII[default]orGMII.

MRCLKH1I

MACSEL[1:0]dependent.

ThispinisEMACcarriersense(MCRS)(I)forMII[default]orGMII,orEMAC

MCRS/RMCRSDVJ4I/O/Zcarriersense/receivedatavalid(RMCRSDV)(I)forRMII.MACSEL[1:0]

dependent.

ThispinisEMACreceiveerror(MRXIR)(I)forMII[default],RMII,orGMII.

MRXER/RMRXERH4I

MACSEL[1:0]dependent.

ThispinisEMACMII[default]orGMIIreceivedatavalid(MRXDV)(I).

MRXDVH5I

MACSEL[1:0]dependent.

MRXD7M2

MRXD6H2

MRXD5L2

EMACreceivedatabusforMII[default],RMII,orGMII

MRXD4L1

I

ThesepinsfunctionasEMACreceivedatapinsforMII[default],RMII,orGMII

MRXD3J3

(MRXD[x:0])(I).MACSEL[1:0]dependent.

MRXD2J1

MRXD1/RMRXD1H3

MRXD0/RMRXD0J2

GMTCLKK5O/ZThispinisEMACGMIItransmitclock(GMTCLK)(O).MACSEL[1:0]dependent.

ThispiniseitherEMACMII[default]orGMIItransmitclock(MTCLK)(I)orthe

EMACRMIIreferenceclock(RMREFCLK)(I).TheEMACfunctioniscontrolled

MTCLK/RMREFCLKN4I

bytheMACSEL[1:0](AEA[10:9]pins).Formoredetailedinformation,see

Section3,DeviceConfiguration.

DeviceOverview 34SubmitDocumentationFeedback