www.ti.com

PRODUCT PREVIEW

GMTCLK

(Output)

2 3

1

4

4

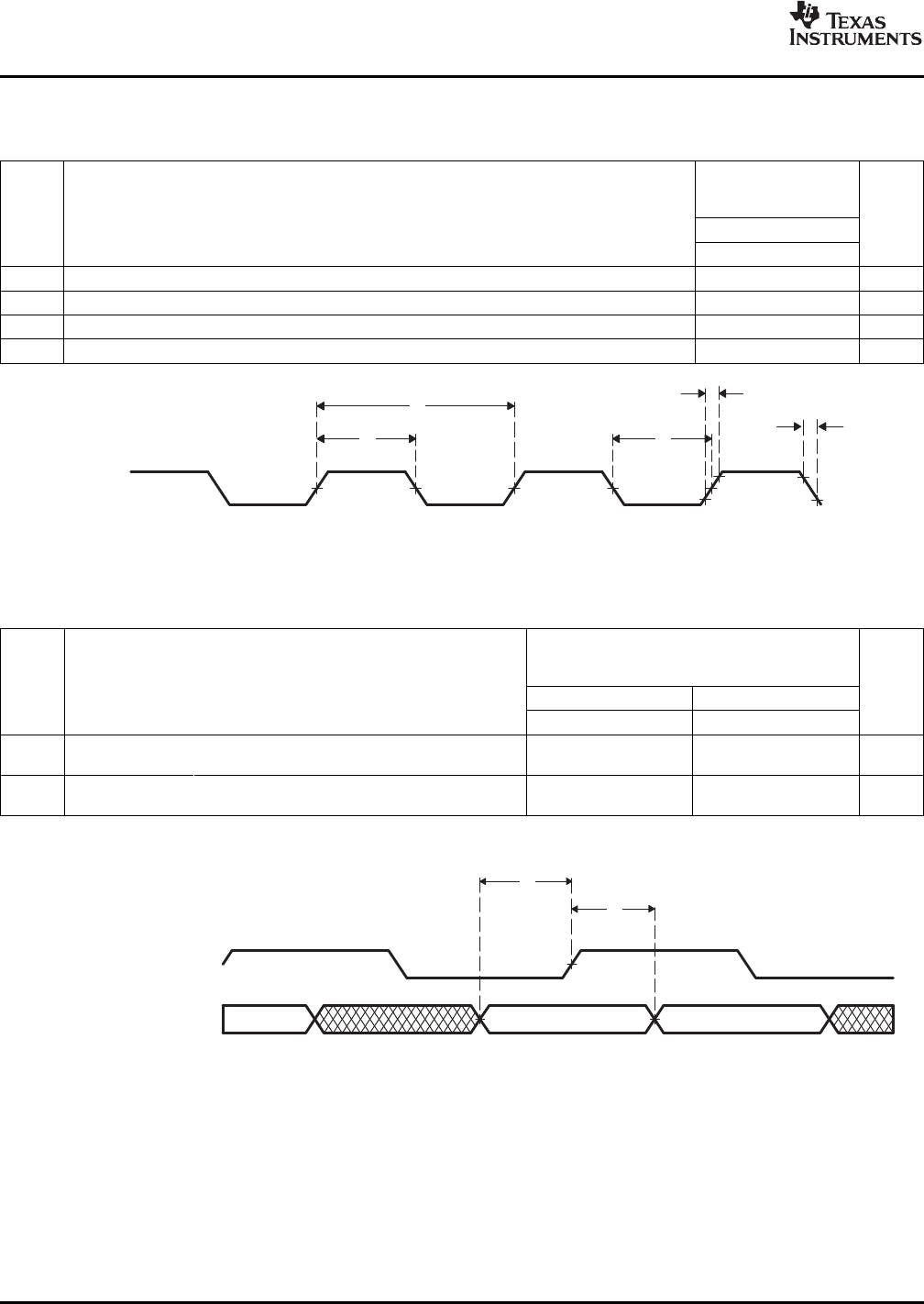

MRCLK (Input)

1

2

MRXD7−MRXD4(GMII only),

MRXD3−MRXD0,

MRXDV, MRXER (Inputs)

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

Table7-77.SwitchingCharacteristicsOverRecommendedOperatingConditionsforGMTCLK-GMII

Operation(seeFigure7-61)

-720

-850

-1000

NO.UNIT

1000Mbps

MINMAX

1t

c(GMTCLK)

Cycletime,GMTCLK8ns

2t

w(GMTCLKH)

Pulseduration,GMTCLKhigh2.8ns

3t

w(GMTCLKL)

Pulseduration,GMTCLKlow2.8ns

4t

t(GMTCLK)

Transitiontime,GMTCLK1ns

Figure7-61.GMTCLKTiming(EMAC–Transmit)[GMIIOperation]

Table7-78.TimingRequirementsforEMACMIIandGMIIReceive10/100/1000Mbit/s

(1)

(seeFigure7-62)

-720

-850

-1000

NO.UNIT

1000Mbps100/10Mbps

MINMAXMINMAX

Setuptime,receiveselectedsignalsvalidbefore

1t

su(MRXD-MRCLKH)

28ns

MRCLKhigh

Holdtime,receiveselectedsignalsvalidafter

2t

h(MRCLKH-MRXD)

08ns

MRCLKhigh

(1)ForMII,Receiveselectedsignalsinclude:MRXD[3:0],MRXDV,andMRXER.ForGMII,Receiveselectedsignalsinclude:MRXD[7:0],

MRXDV,andMRXER.

Figure7-62.EMACReceiveInterfaceTiming[MIIandGMIIOperation]

C64x+PeripheralInformationandElectricalSpecifications 196SubmitDocumentationFeedback