www.ti.com

PRODUCT PREVIEW

3.3PeripheralSelectionAfterDeviceReset

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

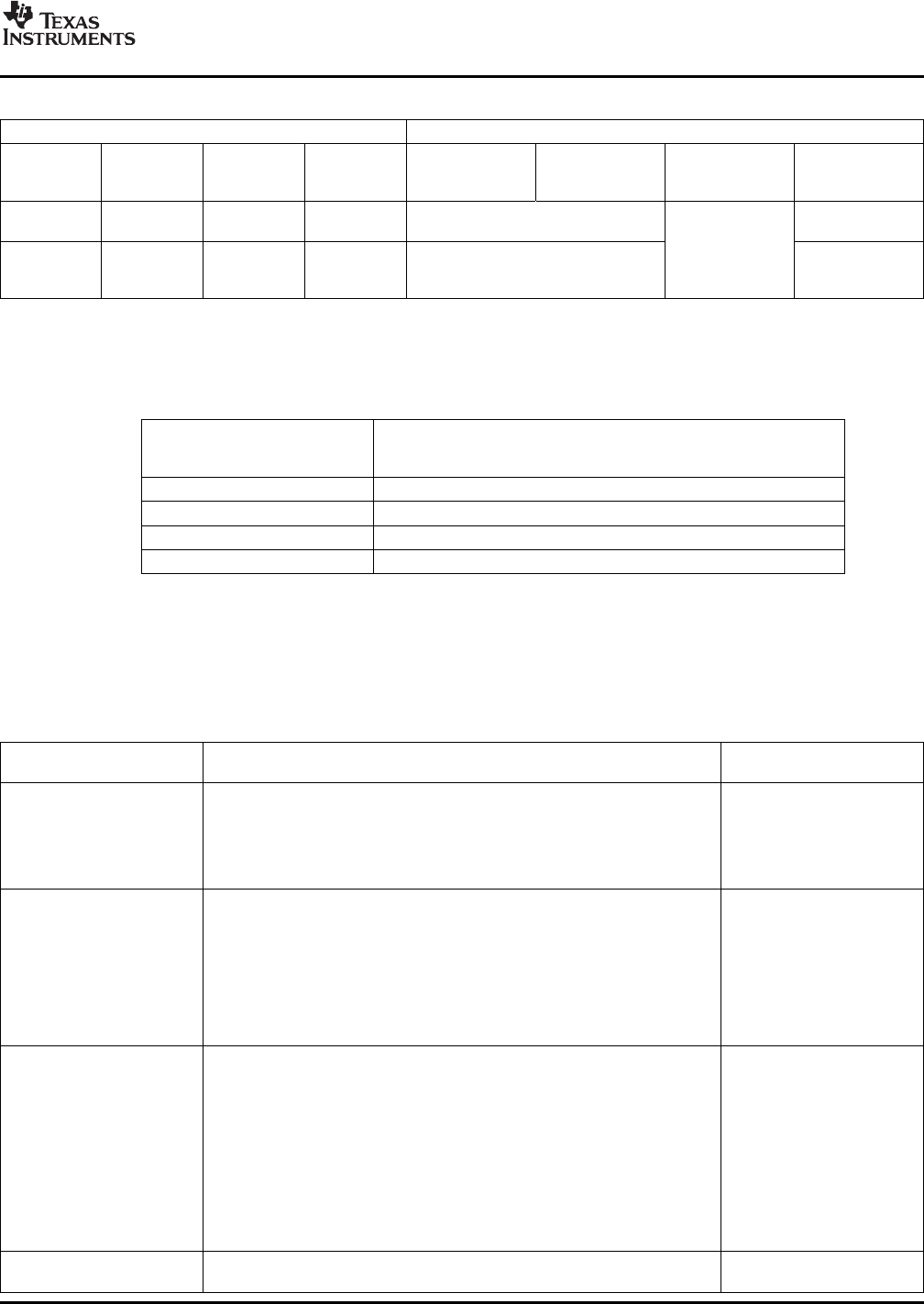

Table3-2.PCI_EN,PCI66,PCI_EEAI,andHPI_WIDTHPeripheralSelection(HPIandPCI)(continued)

CONFIGURATIONPINSETTING

(1)

PERIPHERALFUNCTIONSELECTED

PCI66PCI_EEAIHPI_WIDTH

PCI_ENPINHPIDATAHPIDATA32-BITPCIPCI

AEA6PINAEA8PINAEA14PIN

[Y29]LOWERUPPER(66-/33-MHz)AUTO-INIT

[U27][P25]

(1)

[R25]

Disabled

100XDisabled

(defaultvalues)

Enabled

Enabled

(33MHz)

101XDisabled(viaExternalI2C

EEPROM)

TheMAC_SEL[1:0]configurationpins(AEA[10:9)controlwhichinterfaceisusedbytheEMAC/MDIO.

Table3-3describestheeffectoftheMACSEL[1:0]configurationpins.

Table3-3.MAC_SEL[1:0]PeripheralSelection(EMAC)

MAC_SEL[1:0]/

EMAC/MDIO

AEA[10:9]PINS[M25,M27]

PERIPHERALFUNCTIONSELECTED

CONFIGURATIONPINSETTING

00b10/100EMAC/MDIOwithMIIInterface[default]

01b10/100EMAC/MDIOwithRMIIInterface

10b10/100/1000EMAC/MDIOwithGMIIInterface

11b10/100/1000EMAC/MDIOwithRGMIIInterface

(1)

(1)RGMIIinterfacerequiresa1.5-/1.8-VI/Osupply.

OntheC6454device,peripheralscanbeinoneofseveralstates.ThesestatesarelistedinTable3-4.

Table3-4.PeripheralStates

PERIPHERALSTHATCAN

STATEDESCRIPTION

BEINTHISSTATE

HPI

PCI

PeripheralpinfunctionhasbeencompletelydisabledthroughthedeviceMcBSP1

Staticpowerdown

configurationpins.Peripheralisheldinresetandclockisturnedoff.EMAC/MDIO

EMIFA

DDR2MemoryController

I2C

Timer0

Timer1

GPIO

Peripheralisheldinresetandclockisturnedoff.Defaultstateforall

DisabledEMAC/MDIO

peripheralsnotinstaticpowerdownmode.

McBSP0

McBSP1

HPI

PCI

I2C

Timer0

Timer1

GPIO

MDIO

EMAC/MDIO

EnabledClocktotheperipheralisturnedonandtheperipheralistakenoutofreset.

McBSP0

McBSP1

HPI

PCI

EMIFA

DDR2MemoryController

Notauser-programmablestate.ThisisanintermediatestatewhenAllperipheralsthatcanbein

Enableinprogress

transitioningfromandisabledstatetoanenabledstate.anenabledstate.

SubmitDocumentationFeedbackDeviceConfiguration53