www.ti.com

PRODUCT PREVIEW

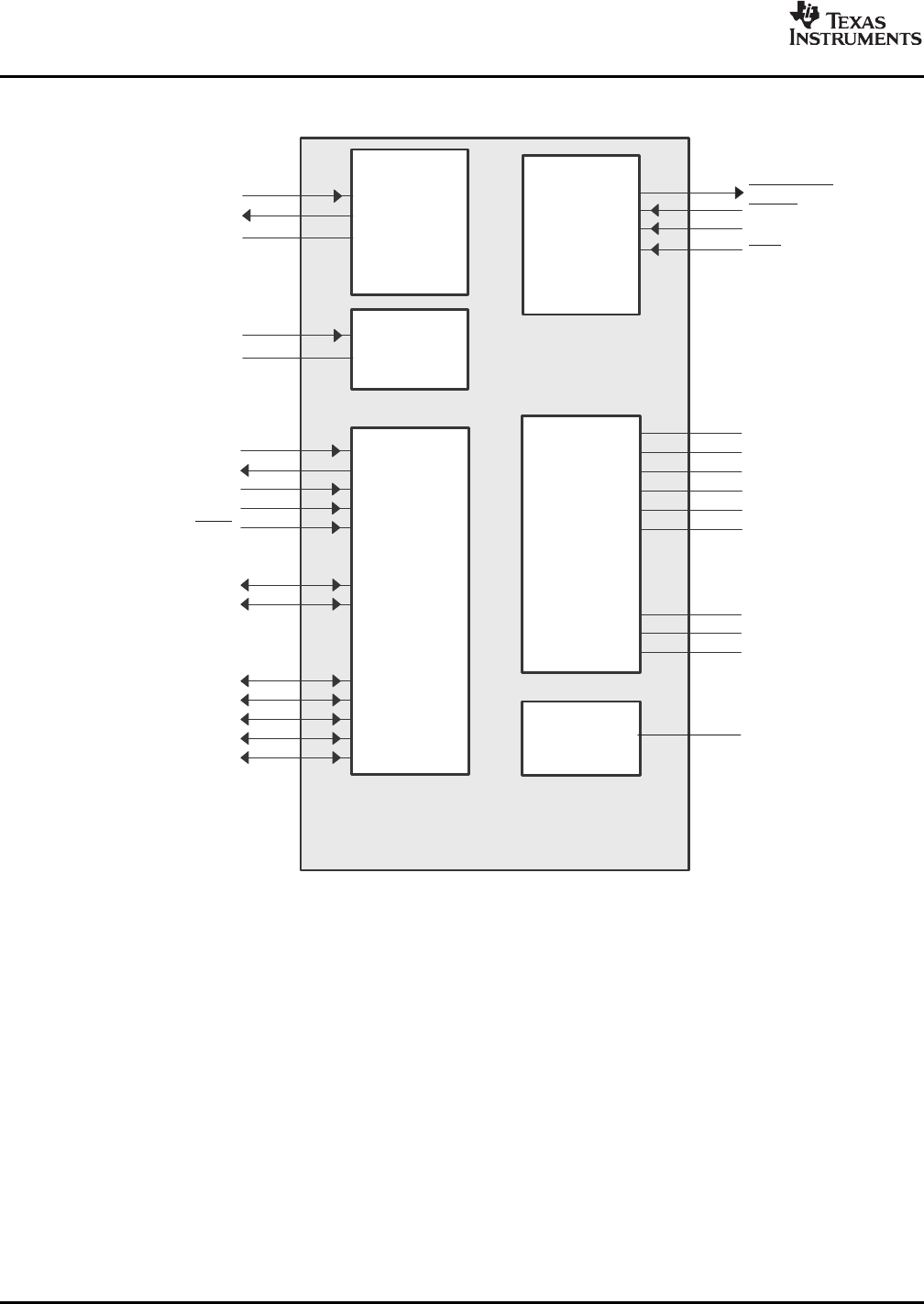

2.6SignalGroupsDescription

TRST

IEEE Standard

1149.1

(JTAG)

Emulation

Reserved

Reset and

Interrupts

Control/Status

TDI

TDO

TMS

TCK

NMI

RESET

RSV03

RSV04

Clock/PLL1

and

PLL Controller

CLKIN1

EMU0

EMU1

SYSCLK4/GP[1]

(A)

EMU14

EMU15

EMU16

EMU17

RSV02

EMU18

RSV06

RSV07

RSV05

RSV77

RSV78

RSV76

•

•

•

•

•

•

RESETSTAT

CLKIN2

POR

PCI_EN

Peripheral

Enable/Disable

Clock/PLL2

PLLV2

PLLV1

A. This pin functions as GP[1] by default. For more details, see the Device Configuration section of this document.

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

Figure2-6.CPUandPeripheralSignals

DeviceOverview 18SubmitDocumentationFeedback