www.ti.com

PRODUCT PREVIEW

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

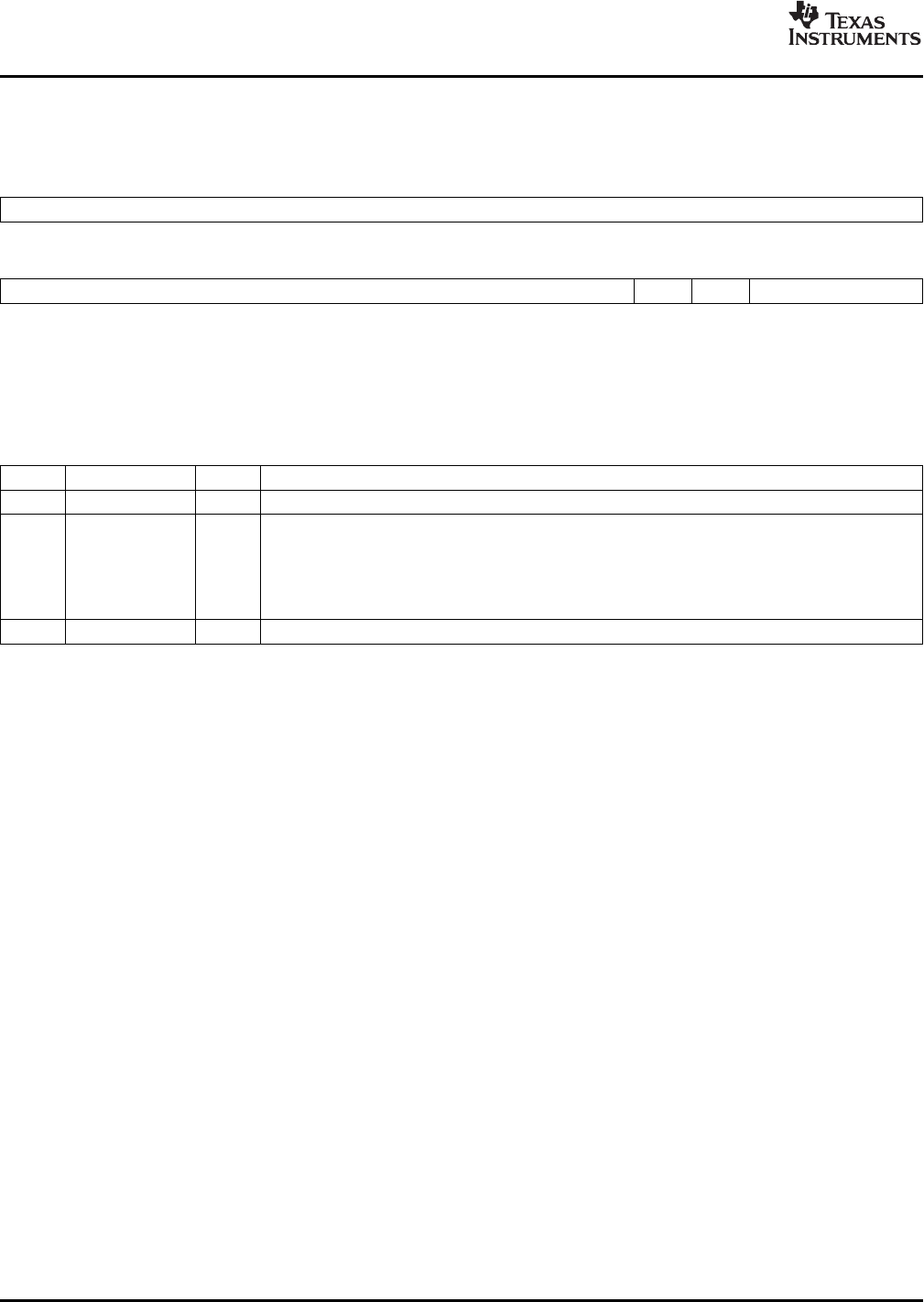

7.7.3.8PLLControllerClockAlignControlRegister

ThePLLcontrollerclockaligncontrolregister(ALNCTL)isshowninFigure7-18anddescribedin

Table7-26.

3116

Reserved

R-0

1554320

ReservedALN5ALN4Reserved

R-0R-1R-1R-1

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Figure7-18.PLLControllerClockAlignControlRegister(ALNCTL)[HexAddress:029A0140]

Table7-26.PLLControllerClockAlignControlRegister(ALNCTL)FieldDescriptions

BitFieldValueDescription

31:5Reserved0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

4:3ALNnSYSCLKnalignment.Donotchangethedefaultvaluesofthesefields.

0DonotalignSYSCLKntootherSYSCLKsduringGOoperation.IfSYSninDCHANGEissetto1,

SYSCLKnswitchestothenewratioimmediatelyaftertheGOSETbitinPLLCMDisset.

1AlignSYSCLKntootherSYSCLKsselectedinALNCTLwhentheGOSETbitinPLLCMDisset.

TheSYSCLKnratioissettotheratioprogrammedintheRATIObitinPLLDIVn.

2:0Reserved0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

C64x+PeripheralInformationandElectricalSpecifications 134SubmitDocumentationFeedback