www.ti.com

PRODUCT PREVIEW

7.13.2McBSPElectricalData/Timing

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

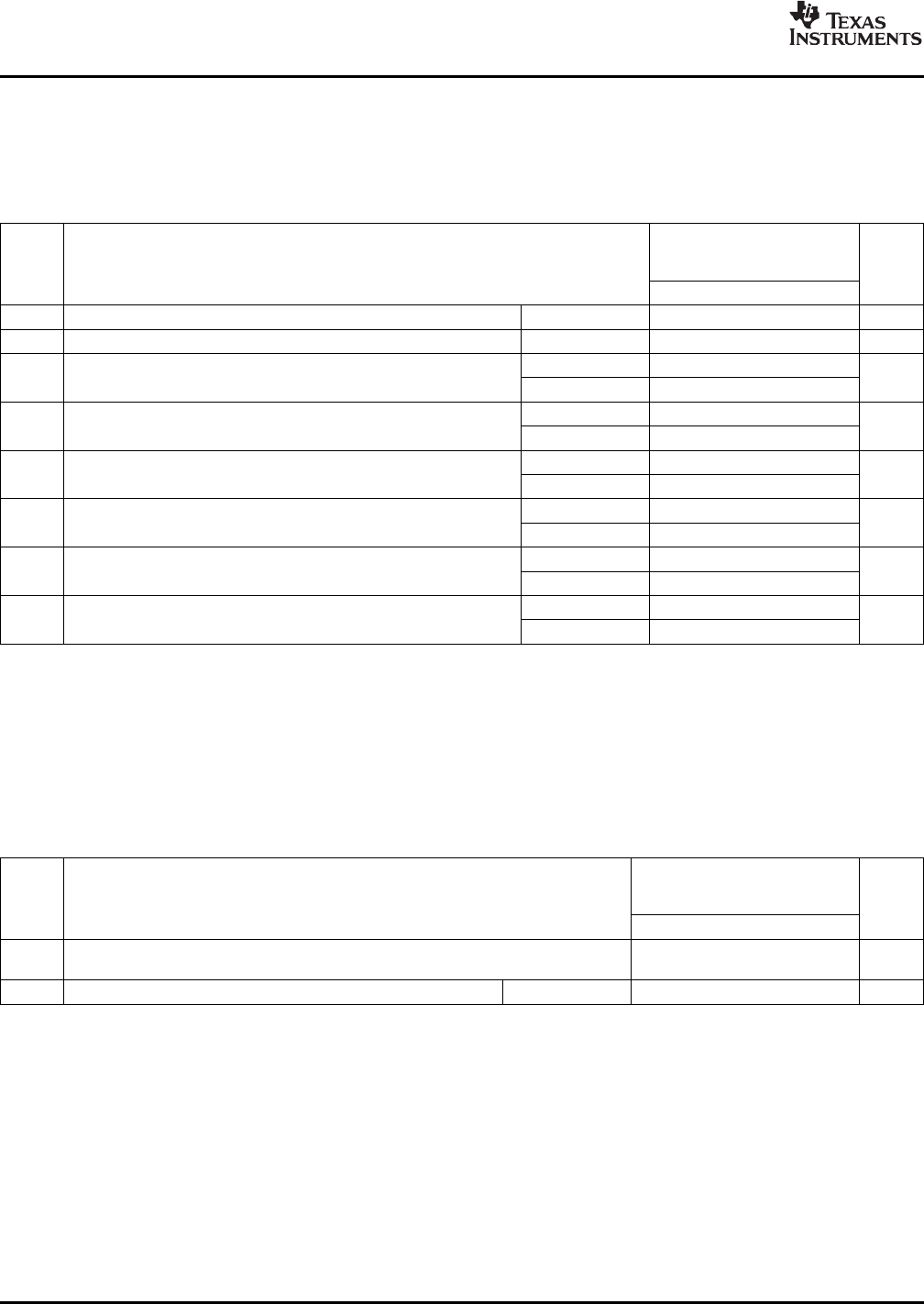

7.13.2.1MultichannelBufferedSerialPort(McBSP)Timing

Table7-59.TimingRequirementsforMcBSP

(1)

(seeFigure7-52)

-720

-850

NO.UNIT

-1000

MINMAX

2t

c(CKRX)

Cycletime,CLKR/XCLKR/Xext6Por10

(2)(3)

ns

3t

w(CKRX)

Pulseduration,CLKR/XhighorCLKR/XlowCLKR/Xext0.5t

c(CKRX)

–1

(4)

ns

CLKRint9

5t

su(FRH-CKRL)

Setuptime,externalFSRhighbeforeCLKRlowns

CLKRext1.3

CLKRint6

6t

h(CKRL-FRH)

Holdtime,externalFSRhighafterCLKRlowns

CLKRext3

CLKRint8

7t

su(DRV-CKRL)

Setuptime,DRvalidbeforeCLKRlowns

CLKRext0.9

CLKRint3

8t

h(CKRL-DRV)

Holdtime,DRvalidafterCLKRlowns

CLKRext3.1

CLKXint9

10t

su(FXH-CKXL)

Setuptime,externalFSXhighbeforeCLKXlowns

CLKXext1.3

CLKXint6

11t

h(CKXL-FXH)

Holdtime,externalFSXhighafterCLKXlowns

CLKXext3

(1)CLKRP=CLKXP=FSRP=FSXP=0.Ifpolarityofanyofthesignalsisinverted,thenthetimingreferencesofthatsignalarealso

inverted.

(2)P=1/CPUclockfrequencyinns.Forexample,whenrunningpartsat1000MHz,useP=1ns.

(3)Usewhichevervalueisgreater.MinimumCLKR/Xcycletimesmustbemet,evenwhenCLKR/Xisgeneratedbyaninternalclock

source.TheminimumCLKR/Xcycletimesarebasedoninternallogicspeed;themaximumusablespeedmaybelowerduetoEDMA

limitationsandACtimingrequirements.

(4)ThisparameterappliestothemaximumMcBSPfrequency.Operateserialclocks(CLKR/X)inthereasonablerangeof40/60dutycycle.

Table7-60.SwitchingCharacteristicsOverRecommendedOperatingConditionsforMcBSP

(1)(2)

(seeFigure7-52)

-720

-850

NO.PARAMETERUNIT

-1000

MINMAX

Delaytime,CLKShightoCLKR/XhighforinternalCLKR/X

1t

d(CKSH-CKRXH)

1.410ns

generatedfromCLKSinput

(3)

2t

c(CKRX)

Cycletime,CLKR/XCLKR/Xint6Por10

(4)(5)(6)

ns

(1)CLKRP=CLKXP=FSRP=FSXP=0.Ifpolarityofanyofthesignalsisinverted,thenthetimingreferencesofthatsignalarealso

inverted.

(2)Minimumdelaytimesalsorepresentminimumoutputholdtimes.

(3)TheCLKSsignalissharedbybothMcBSP0andMcBSP1onthisdevice.

(4)MinimumCLKR/Xcycletimesmustbemet,evenwhenCLKR/Xisgeneratedbyaninternalclocksource.MinimumCLKR/Xcycletimes

arebasedoninternallogicspeed;themaximumusablespeedmaybelowerduetoEDMAlimitationsandACtimingrequirements.

(5)P=1/CPUclockfrequencyinns.Forexample,whenrunningpartsat1000MHz,useP=1ns.

(6)Usewhichevervalueisgreater.

C64x+PeripheralInformationandElectricalSpecifications 180SubmitDocumentationFeedback