www.ti.com

PRODUCT PREVIEW

7.9.2DDR2MemoryControllerPeripheralRegisterDescription(s)

7.9.3DDR2MemoryControllerElectricalData/Timing

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

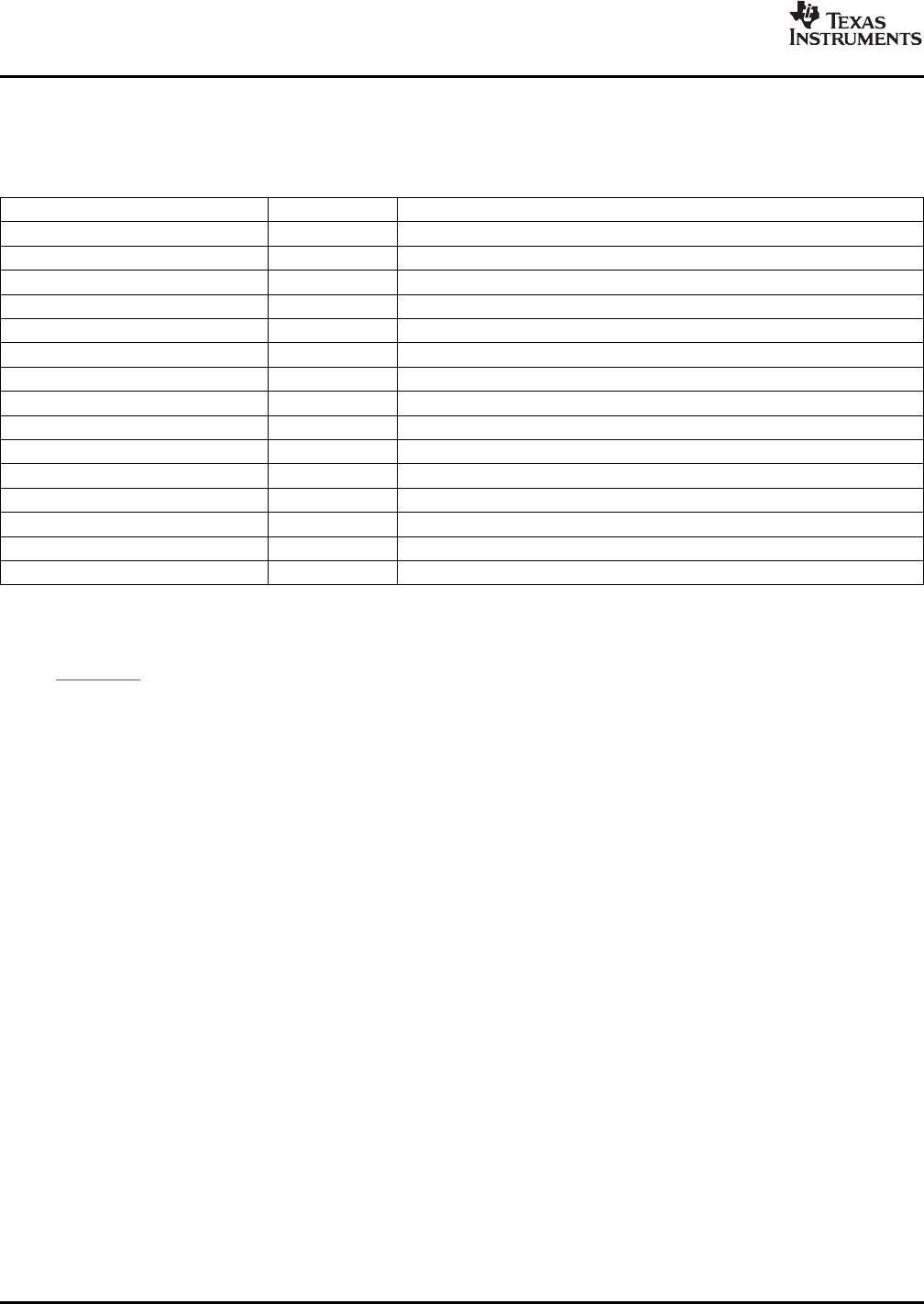

Table7-40.DDR2MemoryControllerRegisters

HEXADDRESSRANGEACRONYMREGISTERNAME

78000000MIDRDDR2MemoryControllerModuleandRevisionRegister

78000004DMCSTATDDR2MemoryControllerStatusRegister

78000008SDCFGDDR2MemoryControllerSDRAMConfigurationRegister

7800000CSDRFCDDR2MemoryControllerSDRAMRefreshControlRegister

78000010SDTIM1DDR2MemoryControllerSDRAMTiming1Register

78000014SDTIM2DDR2MemoryControllerSDRAMTiming2Register

78000018-Reserved

78000020BPRIODDR2MemoryControllerBurstPriorityRegister

78000024-7800004C-Reserved

78000050-78000078-Reserved

7800007C-780000BC-Reserved

780000C0-780000E0-Reserved

780000E4DMCCTLDDR2MemoryControllerControlRegister

780000E8-780000FC-Reserved

78000100-7FFFFFFF-Reserved

TheImplementingDDR2PCBLayoutontheTMS320C6454applicationreport(literaturenumber

SPRAAA7)specifiesacompleteDDR2interfacesolutionfortheC6454aswellasalistofcompatible

DDR2devices.TIhasperformedthesimulationandsystemcharacterizationtoensureallDDR2interface

timingsinthissolutionaremet;therefore,noelectricaldata/timinginformationissuppliedhereforthis

interface.

TIonlysupportsdesignsthatfollowtheboarddesignguidelinesoutlinedintheSPRAAA7

applicationreport.

148C64x+PeripheralInformationandElectricalSpecificationsSubmitDocumentationFeedback