www.ti.com

PRODUCT PREVIEW

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

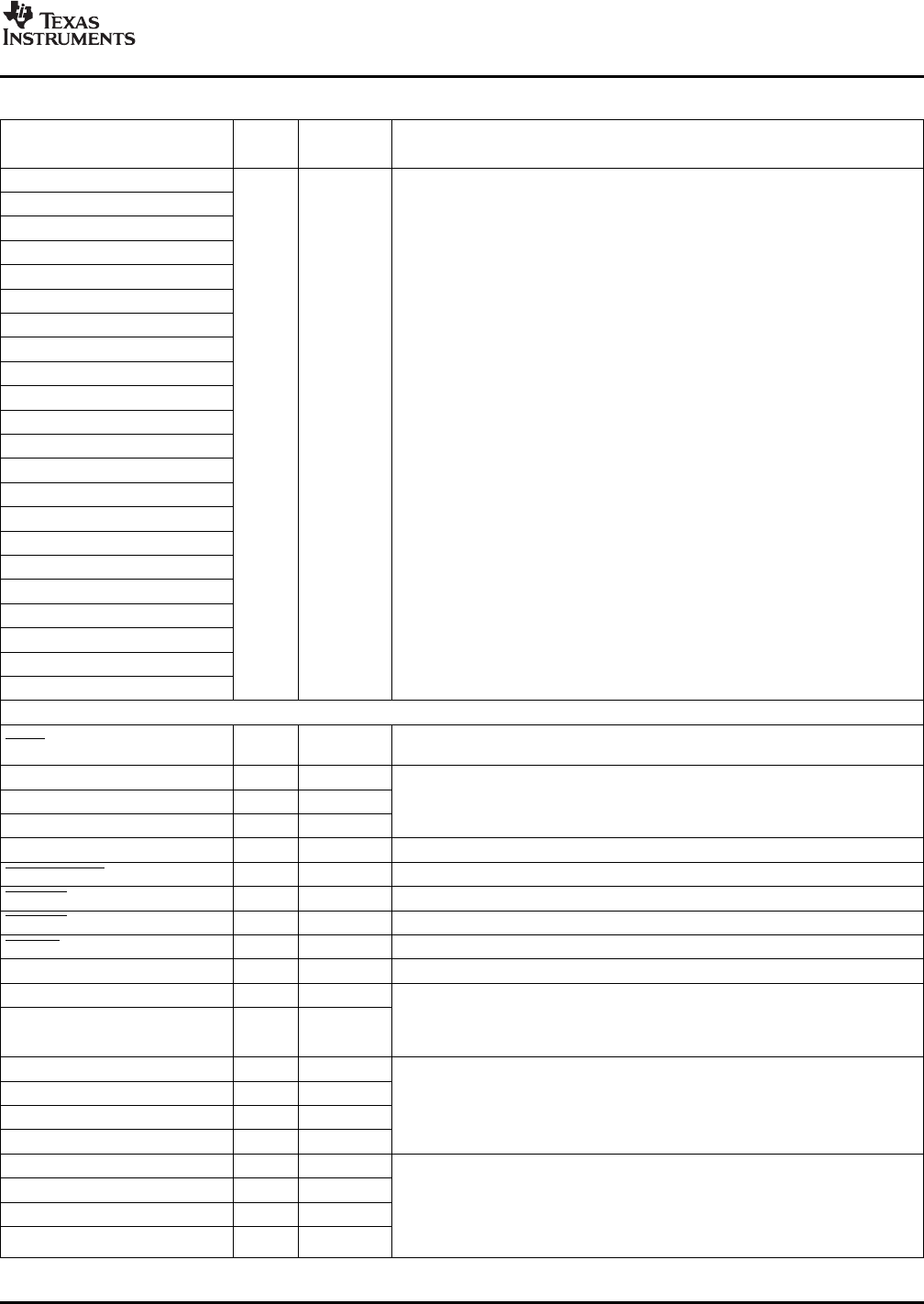

Table2-3.TerminalFunctions(continued)

SIGNAL

TYPE

(1)

IPD/IPU

(2)

DESCRIPTION

NAMENO.

AED21AD29

AED20AJ28

AED19AF29

AED18AH28

AED17AE29

AED16AG28

AED15AF28

AED14AH26

AED13AE28

AED12AE26

AED11AD26

I/O/ZIPUEMIFAexternaldata

AED10AF27

AED9AG27

AED8AD27

AED7AE25

AED6AJ27

AED5AJ26

AED4AE27

AED3AG25

AED2AH27

AED1AF25

AED0AD25

DDR2MEMORYCONTROLLER(32-BIT)-CONTROLSIGNALSCOMMONTOALLTYPESOFMEMORY

DDR2MemoryControllermemoryspaceenable.WhentheDDR2Memory

DCE0E14O/Z

Controllerisenabled,italwayskeepsthispinlow.

DBA2E15O/Z

DBA1D15O/ZDDR2MemoryControllerbankaddresscontrol

DBA0C15O/Z

DDR2CLKOUTB14O/ZDDR2MemoryControlleroutputclock(CLKIN2frequency×10)

DDR2CLKOUTA14O/ZNegativeDDR2MemoryControlleroutputclock(CLKIN2frequency×10)

DSDCASD13O/ZDDR2MemoryControllerSDRAMcolumn-addressstrobe

DSDRASC13O/ZDDR2MemoryControllerSDRAMrow-addressstrobe

DSDWEB13O/ZDDR2MemoryControllerSDRAMwrite-enable

DSDCKED14O/ZDDR2MemoryControllerSDRAMclock-enable(usedforself-refreshmode).

DEODT1A17O/ZOn-dieterminationsignalstoexternalDDR2SDRAM.Thesepinsshouldnotbe

connectedtotheDDR2SDRAM.

Note:Therearenoon-dieterminationresistorsimplementedontheC6454

DEODT0E16O/Z

DSPdie.

DSDDQGATE3F21I

DDR2MemoryControllerdatastrobegate[3:0]

DSDDQGATE2E21O/Z

Forhookupofthesesignals,pleaserefertotheImplementingDDR2PCB

LayoutonaTMS320C6454HardwareDesignApplicationReport(literature

DSDDQGATE1B9I

numberSPRAAA9).

DSDDQGATE0A9O/Z

DSDDQM3C23O/ZDDR2MemoryControllerbyte-enablecontrols

•Decodedfromthelow-orderaddressbits.Thenumberofaddressbitsor

DSDDQM2C20O/Z

byteenablesuseddependsonthewidthofexternalmemory.

DSDDQM1C8O/Z

•Byte-writeenablesformosttypesofmemory.

DSDDQM0C11O/Z

•CanbedirectlyconnectedtoSDRAMreadandwritemasksignal(SDQM).

SubmitDocumentationFeedbackDeviceOverview31