www.ti.com

PRODUCT PREVIEW

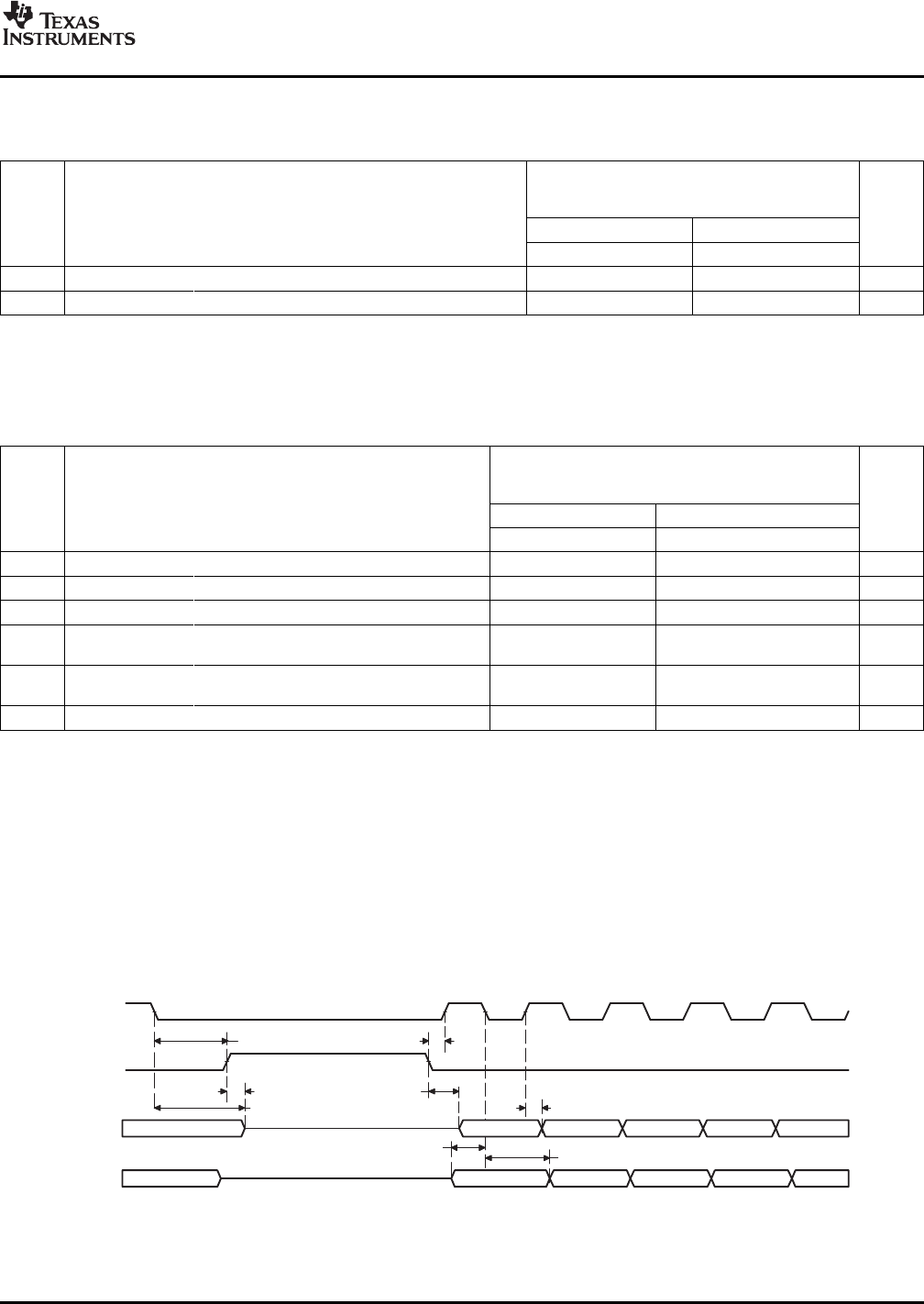

Bit 0 Bit(n-1) (n-2) (n-3) (n-4)

Bit 0 Bit(n-1) (n-2) (n-3) (n-4)

5

4

3

8

7

6

21

CLKX

FSX

DX

DR

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

Table7-62.TimingRequirementsforMcBSPasSPIMasterorSlave:CLKSTP=10b,CLKXP=0

(1)(2)

(seeFigure7-54)

-720

-850

-1000

NO.UNIT

MASTERSLAVE

MINMAXMINMAX

4t

su(DRV-CKXL)

Setuptime,DRvalidbeforeCLKXlow122–18Pns

5t

h(CKXL-DRV)

Holdtime,DRvalidafterCLKXlow45+36Pns

(1)P=1/CPUclockfrequencyinns.Forexample,whenrunningpartsat1000MHz,useP=1ns.

(2)ForallSPISlavemodes,CLKGisprogrammedas1/6oftheCPUclockbysettingCLKSM=CLKGDV=1.

Table7-63.SwitchingCharacteristicsOverRecommendedOperatingConditionsforMcBSPasSPI

MasterorSlave:CLKSTP=10b,CLKXP=0

(1)(2)

(seeFigure7-54)

-720

-850

-1000

NO.PARAMETERUNIT

MASTER

(3)

SLAVE

MINMAXMINMAX

1t

h(CKXL-FXL)

Holdtime,FSXlowafterCLKXlow

(4)

T–2T+3ns

2t

d(FXL-CKXH)

Delaytime,FSXlowtoCLKXhigh

(5)

L–2L+3ns

3t

d(CKXH-DXV)

Delaytime,CLKXhightoDXvalid–2418P+2.830P+17ns

Disabletime,DXhighimpedancefollowing

6t

dis(CKXL-DXHZ)

L–2L+3ns

lastdatabitfromCLKXlow

Disabletime,DXhighimpedancefollowing

7t

dis(FXH-DXHZ)

6P+318P+17ns

lastdatabitfromFSXhigh

8t

d(FXL-DXV)

Delaytime,FSXlowtoDXvalid12P+224P+17ns

(1)P=1/CPUclockfrequencyinns.Forexample,whenrunningpartsat1000MHz,useP=1ns.

(2)ForallSPISlavemodes,CLKGisprogrammedas1/6oftheCPUclockbysettingCLKSM=CLKGDV=1.

(3)S=Samplerategeneratorinputclock=6PifCLKSM=1(P=1/CPUclockfrequency)

S=Samplerategeneratorinputclock=P_clksifCLKSM=0(P_clks=CLKSperiod)

T=CLKXperiod=(1+CLKGDV)*S

H=CLKXhighpulsewidth=(CLKGDV/2+1)*SifCLKGDViseven

H=(CLKGDV+1)/2*SifCLKGDVisodd

L=CLKXlowpulsewidth=(CLKGDV/2)*SifCLKGDViseven

L=(CLKGDV+1)/2*SifCLKGDVisodd

(4)FSRP=FSXP=1.AsaSPIMaster,FSXisinvertedtoprovideactive-lowslave-enableoutput.AsaSlave,theactive-lowsignalinput

onFSXandFSRisinvertedbeforebeingusedinternally.

CLKXM=FSXM=1,CLKRM=FSRM=0forMasterMcBSP

CLKXM=CLKRM=FSXM=FSRM=0forSlaveMcBSP

(5)FSXshouldbelowbeforetherisingedgeofclocktoenableSlavedevicesandthenbeginaSPItransferattherisingedgeoftheMaster

clock(CLKX).

Figure7-54.McBSPTimingasSPIMasterorSlave:CLKSTP=10b,CLKXP=0

SubmitDocumentationFeedbackC64x+PeripheralInformationandElectricalSpecifications183