www.ti.com

PRODUCT PREVIEW

TXC (at DSP)

(B)

TXD[3:0]

(A)

TXCTL

(A)

5

6

1st Half-byte

TXERRTXEN

2nd Half-byte

1

2

Internal TXC

TXC at DSP pins

4

4

2

3

1

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

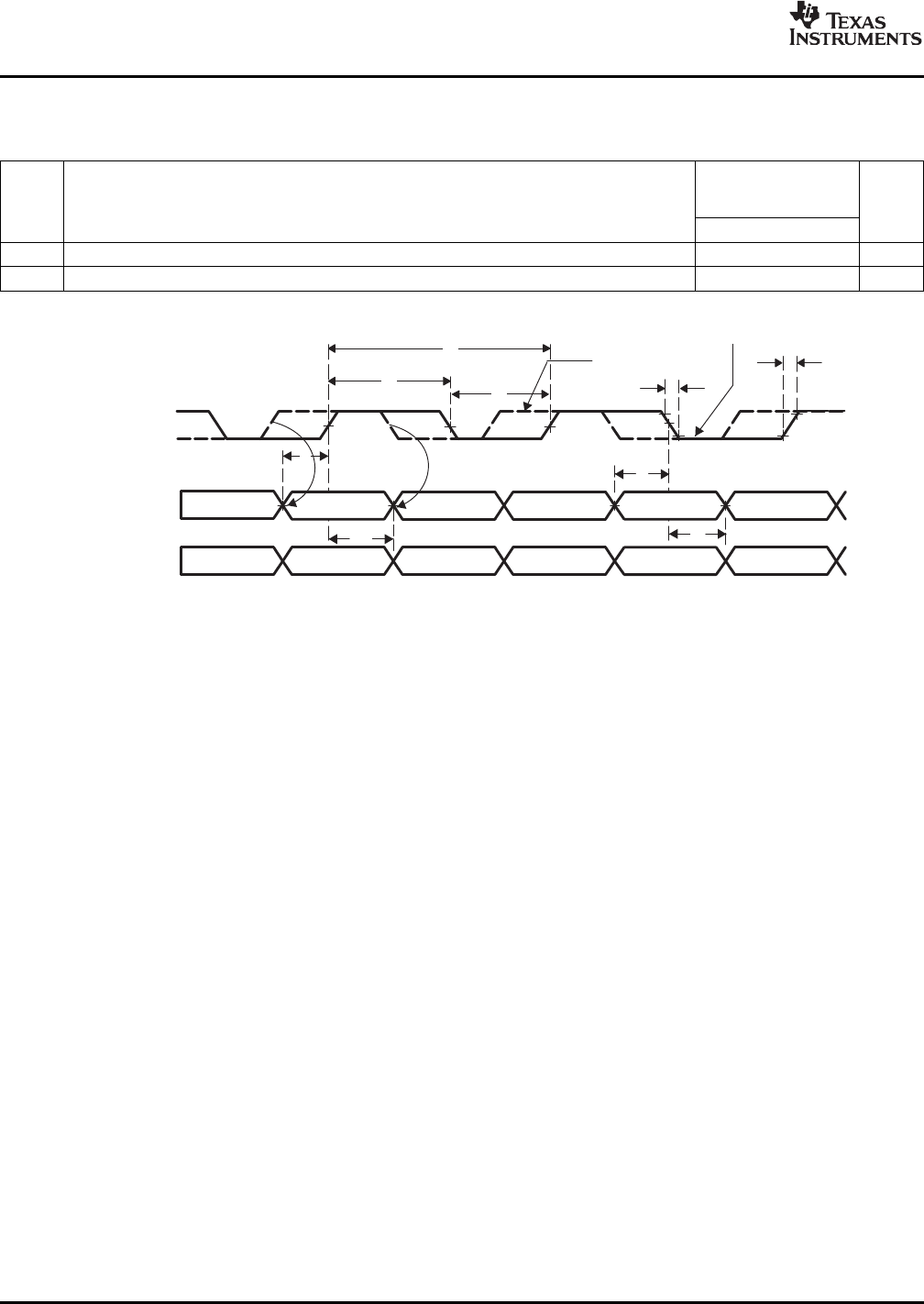

Table7-88.SwitchingCharacteristicsOverRecommendedOperatingConditionsforEMACRGMII

Transmit

(1)

(seeFigure7-70)

-720

-850

NO.PARAMETERUNIT

-1000

MINMAX

5t

su(TXD-TXCH)

Setuptime,transmitselectedsignalsvalidbeforeTXC(atDSP)high/low1.2ns

6t

h(TXCH-TXD)

Holdtime,transmitselectedsignalsvalidafterTXC(atDSP)high/low1.2

(1)ForRGMII,transmitselectedsignalsinclude:TXD[3:0]andTXCTL.

A.Dataandcontrolinformationistransmittedusingbothedgesoftheclocks.TXD[3:0]carriesdatabits3-0ontherising

edgeofTXCanddatabits7-4onthefallingedgeofTXC.Similarly,TX_CTLcarriesTXENonrisingedgeofTXCand

TXERRoffallingedge.

B.TXCisdelayedinternallybeforebeingdriventotheTXCpin.

Figure7-70.EMACTransmitInterfaceTiming[RGMIIOperation]

(A)(B)

202C64x+PeripheralInformationandElectricalSpecificationsSubmitDocumentationFeedback