www.ti.com

PRODUCT PREVIEW

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

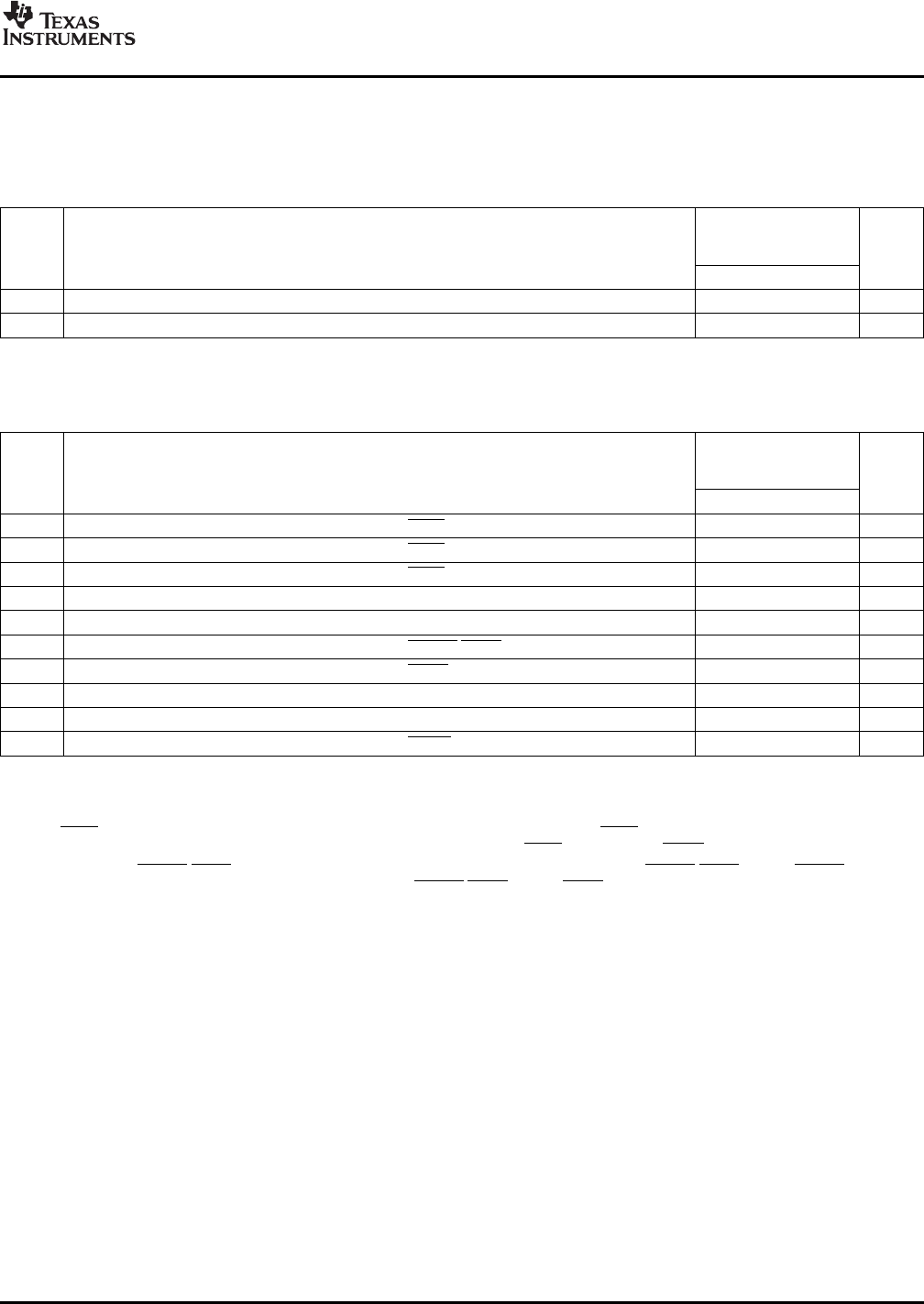

7.10.3.2ProgrammableSynchronousInterfaceTiming

Table7-46.TimingRequirementsforProgrammableSynchronousInterfaceCyclesforEMIFAModule

(seeFigure7-36)

-720

-850

NO.UNIT

-1000

MINMAX

6t

su(EDV-EKOH)

Setuptime,readAEDxvalidbeforeAECLKOUThigh2ns

7t

h(EKOH-EDV)

Holdtime,readAEDxvalidafterAECLKOUThigh1.5ns

Table7-47.SwitchingCharacteristicsOverRecommendedOperatingConditionsforProgrammable

SynchronousInterfaceCyclesforEMIFAModule

(1)

(seeFigure7-36–Figure7-38)

-720

-850

NO.PARAMETERUNIT

-1000

MINMAX

1t

d(EKOH-CEV)

Delaytime,AECLKOUThightoACExvalid1.34.9ns

2t

d(EKOH-BEV)

Delaytime,AECLKOUThightoABExvalid4.9ns

3t

d(EKOH-BEIV)

Delaytime,AECLKOUThightoABExinvalid1.3ns

4t

d(EKOH-EAV)

Delaytime,AECLKOUThightoAEAxvalid4.9ns

5t

d(EKOH-EAIV)

Delaytime,AECLKOUThightoAEAxinvalid1.3ns

8t

d(EKOH-ADSV)

Delaytime,AECLKOUThightoASADS/ASREvalid1.34.9ns

9t

d(EKOH-OEV)

Delaytime,AECLKOUThightoASOEvalid1.34.9ns

10t

d(EKOH-EDV)

Delaytime,AECLKOUThightoAEDxvalid4.9ns

11t

d(EKOH-EDIV)

Delaytime,AECLKOUThightoAEDxinvalid1.3ns

12t

d(EKOH-WEV)

Delaytime,AECLKOUThightoASWEvalid1.34.9ns

(1)ThefollowingparametersareprogrammableviatheEMIFACEConfigurationregisters(CEnCFG):

•Readlatency(R_LTNCY):0-,1-,2-,or3-cyclereadlatency

•Writelatency(W_LTNCY):0-,1-,2-,or3-cyclewritelatency

•ACExassertionlength(CE_EXT):ForstandardSBSRAMorZBTSRAMinterface,ACExgoesinactiveafterthefinalcommandhas

beenissued(CE_EXT=0).ForsynchronousFIFOinterfacewithglue,ACExisactivewhenASOEisactive(CE_EXT=1).

•FunctionofASADS/ASRE(R_ENABLE):ForstandardSBSRAMorZBTSRAMinterface,ASADS/ASREactsasASADSwith

deselectcycles(R_ENABLE=0).ForFIFOinterface,ASADS/ASREactsasASREwithNOdeselectcycles(R_ENABLE=1).

SubmitDocumentationFeedbackC64x+PeripheralInformationandElectricalSpecifications155