www.ti.com

PRODUCT PREVIEW

EMAC

HPI

M

M

128-bit

(SYSCLK2)

M3

M0

S

M

M

M

McBSPsS

DDR2

Memory

Controller

S

EMIFAS

PCI

S

MASTER

SM

Bridge

CFG

SCR

S

Bridge

PCI M

EDMA3 Channel

Controller

EDMA3

Transfer

Controllers

Megamodule

M1

M2

S3

S0

S1

S2

S S

Events

MMegamodule

Data SCR

128 (SYSCLK2)

128 (SYSCLK2)

128 (SYSCLK2)

128 (SYSCLK2)

32 (SYSCLK3)

32

(SYSCLK3)

32 (SYSCLK3)

32

(SYSCLK3)

128 (SYSCLK2)

128 (SYSCLK2)

Bridge

128

(SYSCLK3)

Bridge

Bridge

128

(SYSCLK2)

128

(SYSCLK2)

64

(SYSCLK2)

64

(SYSCLK2)

32 (SYSCLK2)

Configuration Bus

Data Bus

128

(SYSCLK2)

M

32 (SYSCLK3)

128 (SYSCLK2)

32

(SYSCLK3)

32 (SYSCLK3)

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

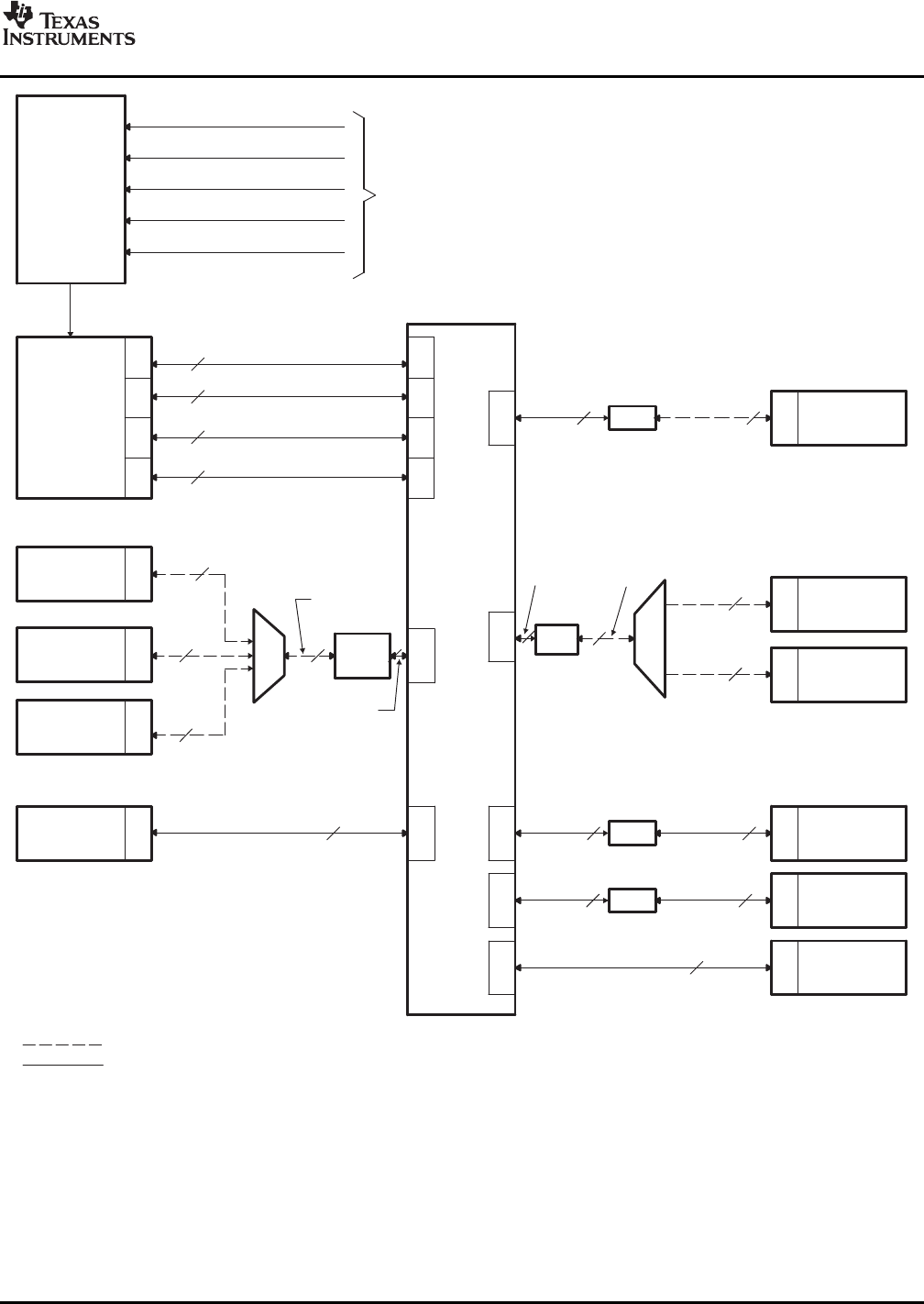

Figure4-1.SwitchedCentralResourceBlockDiagram

SubmitDocumentationFeedbackSystemInterconnect73