www.ti.com

PRODUCT PREVIEW

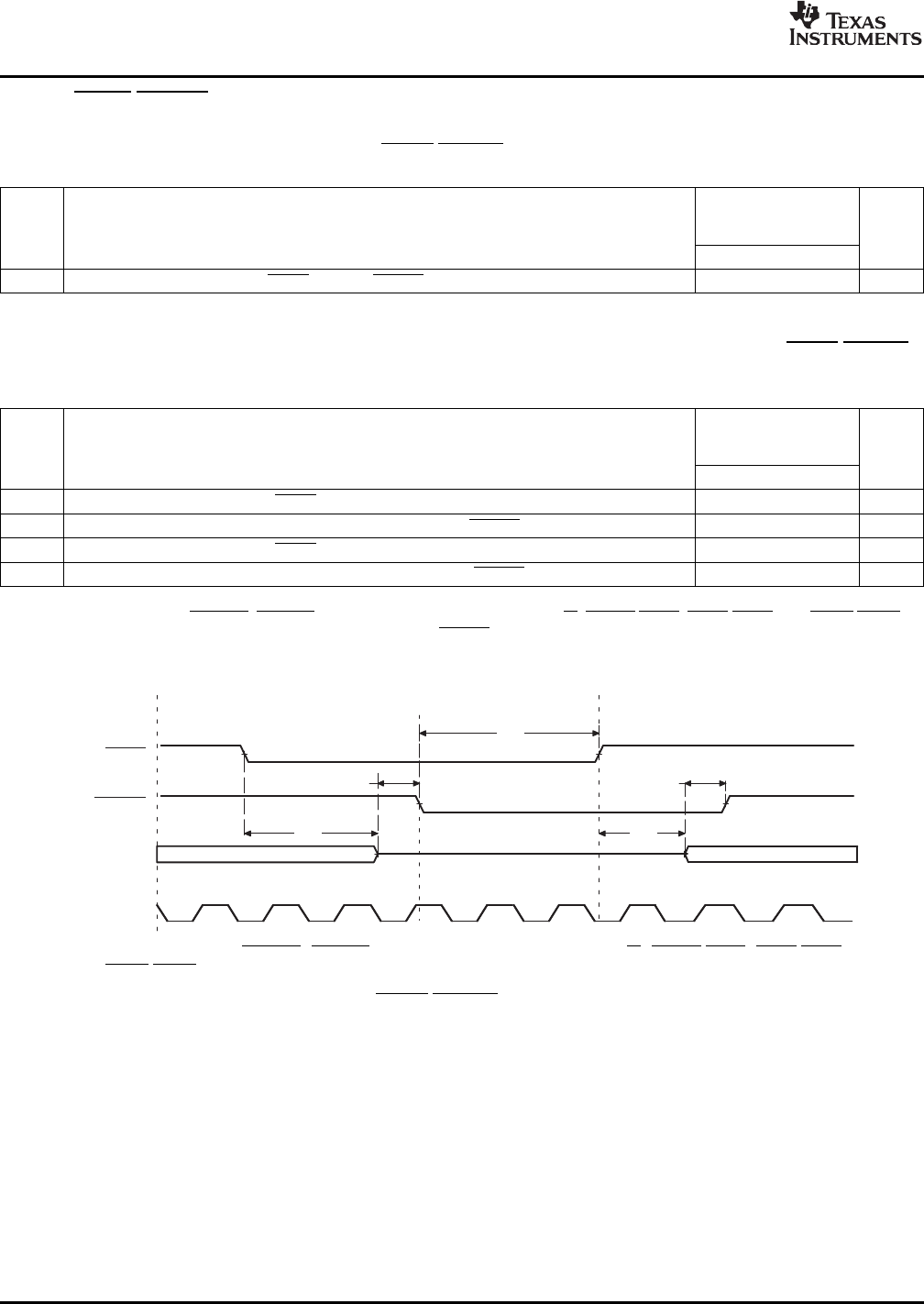

7.10.4HOLD/HOLDATiming

HOLD

HOLDA

EMIF Bus

(A)

DSP Owns Bus

External Requestor

Owns Bus

DSP Owns Bus

DSP DSP

1

3

2 5

4

AECLKOUT

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

Table7-48.TimingRequirementsfortheHOLD/HOLDACyclesforEMIFAModule

(1)

(seeFigure7-39)

-720

-850

NO.UNIT

-1000

MINMAX

3t

h(HOLDAL-HOLDL)

Holdtime,HOLDlowafterHOLDAlowEns

(1)E=theEMIFinputclock(ECLKIN)periodinnsforEMIFA.

Table7-49.SwitchingCharacteristicsOverRecommendedOperatingConditionsfortheHOLD/HOLDA

CyclesforEMIFAModule

(1)(2)

(seeFigure7-39)

-720

-850

NO.PARAMETERUNIT

-1000

MINMAX

1t

d(HOLDL-EMHZ)

Delaytime,HOLDlowtoEMIFABushighimpedance2E

(3)

ns

2t

d(EMHZ-HOLDAL)

Delaytime,EMIFBushighimpedancetoHOLDAlow02Ens

4t

d(HOLDH-EMLZ)

Delaytime,HOLDhightoEMIFBuslowimpedance2E7Ens

5t

d(EMLZ-HOLDAH)

Delaytime,EMIFABuslowimpedancetoHOLDAhigh02Ens

(1)E=theEMIFinputclock(ECLKIN)periodinnsforEMIFA.

(2)EMIFABusconsistsof:ACE[5:2],ABE[7:0],AED[63:0],AEA[19:0],ABA[1:0],AR/W,ASADS/ASRE,AAOE/ASOE,andAAWE/ASWE.

(3)AllpendingEMIFtransactionsareallowedtocompletebeforeHOLDAisasserted.Ifnobustransactionsareoccurring,thenthe

minimumdelaytimecanbeachieved.

A.EMIFABusconsistsof:ACE[5:2],ABE[7:0],AED[63:0],AEA[19:0],ABA[1:0],AR/W,ASADS/ASRE,AAOE/ASOE,

andAAWE/ASWE.

Figure7-39.HOLD/HOLDATimingforEMIFA

158C64x+PeripheralInformationandElectricalSpecificationsSubmitDocumentationFeedback