www.ti.com

PRODUCT PREVIEW

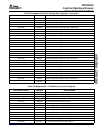

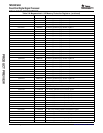

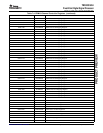

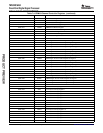

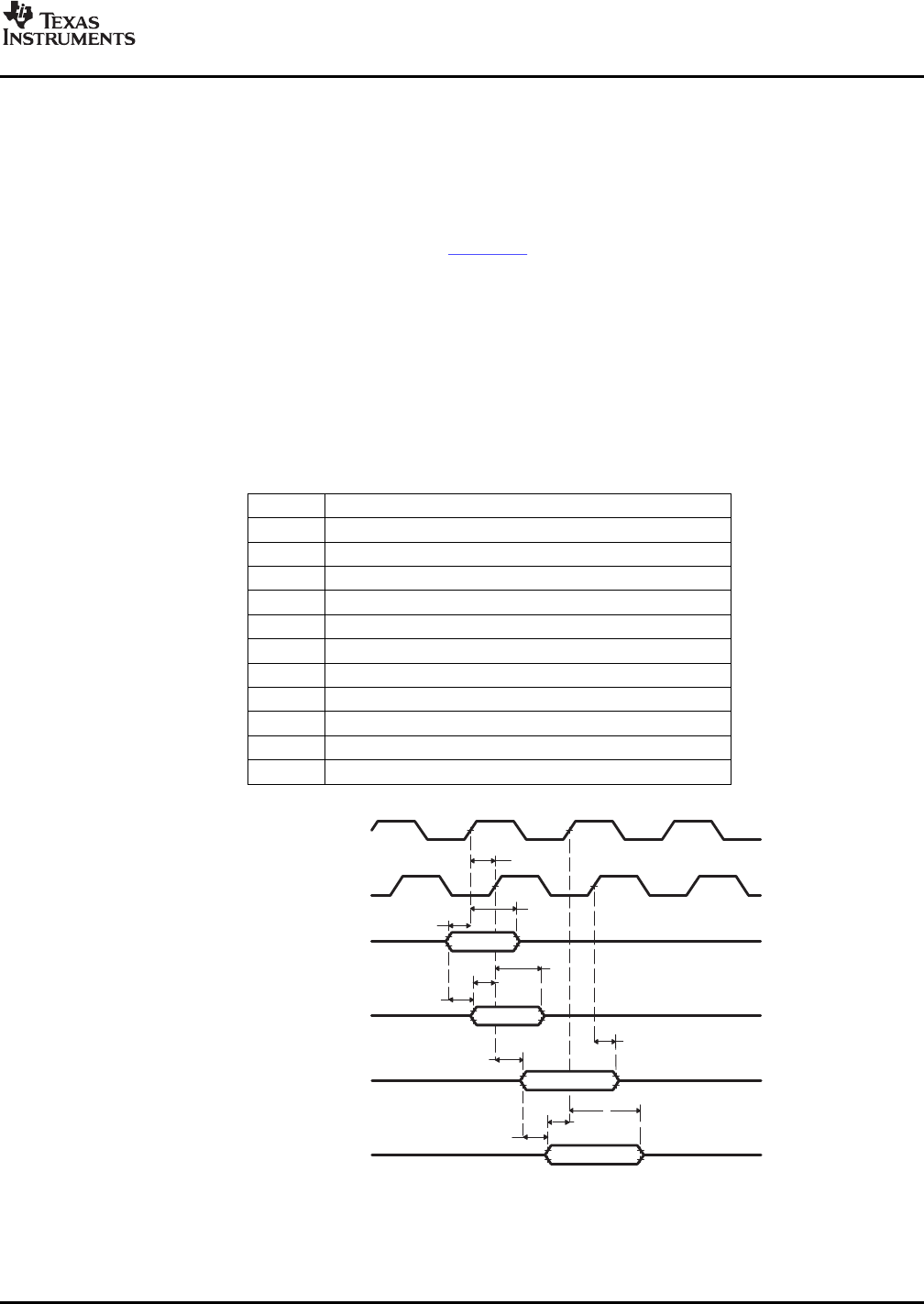

7.1.3TimingParametersandBoardRoutingAnalysis

1

2

3

4

5

6

7

8

10

11

AECLKOUT

(Output from DSP)

AECLKOUT

(Input to External Device)

Control Signals

(A)

(Output from DSP)

Control Signals

(Input to External Device)

Data Signals

(B)

(Output from External Device)

Data Signals

(B)

(Input to DSP)

9

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

Thetimingparametervaluesspecifiedinthisdatasheetdonotincludedelaysbyboardroutings.Asa

goodboarddesignpractice,suchdelaysmustalwaysbetakenintoaccount.Timingvaluesmaybe

adjustedbyincreasing/decreasingsuchdelays.TIrecommendsutilizingtheavailableI/Obuffer

informationspecification(IBIS)modelstoanalyzethetimingcharacteristicscorrectly.ToproperlyuseIBIS

modelstoattainaccuratetiminganalysisforagivensystem,seetheUsingIBISModelsforTiming

Analysisapplicationreport(literaturenumberSPRA839).Ifneeded,externallogichardwaresuchas

buffersmaybeusedtocompensateanytimingdifferences.

Forinputs,timingismostimpactedbytheround-trippropagationdelayfromtheDSPtotheexternal

deviceandfromtheexternaldevicetotheDSP.Thisround-tripdelaytendstonegativelyimpacttheinput

setuptimemargin,butalsotendstoimprovetheinputholdtimemargins(seeTable7-1andFigure7-4).

Figure7-4representsageneraltransferbetweentheDSPandanexternaldevice.Thefigurealso

representsboardroutedelaysandhowtheyareperceivedbytheDSPandtheexternaldevice.

Table7-1.Board-LevelTimingExample

(seeFigure7-4)

NO.DESCRIPTION

1Clockroutedelay

2MinimumDSPholdtime

3MinimumDSPsetuptime

4Externaldeviceholdtimerequirement

5Externaldevicesetuptimerequirement

6Controlsignalroutedelay

7Externaldeviceholdtime

8Externaldeviceaccesstime

9DSPholdtimerequirement

10DSPsetuptimerequirement

11Dataroutedelay

A.ControlsignalsincludedataforWrites.

B.DatasignalsaregeneratedduringReadsfromanexternaldevice.

Figure7-4.Board-LevelInput/OutputTimings

SubmitDocumentationFeedbackC64x+PeripheralInformationandElectricalSpecifications95