www.ti.com

PRODUCT PREVIEW

C64x+tDSP:

C6454

PREFIX

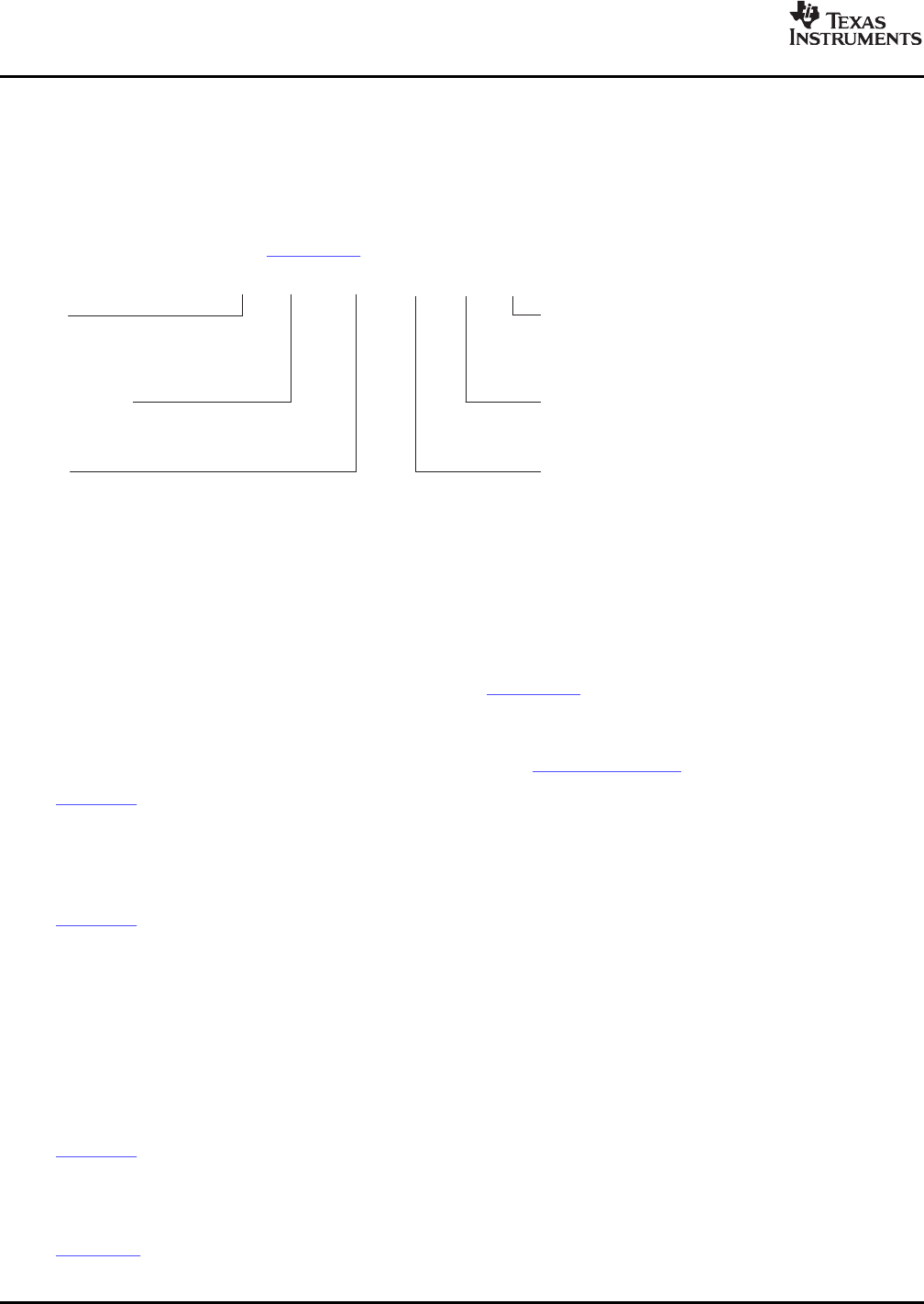

TMX 320 C6454 ZTZ

TMX = Experimental device

TMS = Qualified device

DEVICE FAMILY

320 = TMS320t DSP family

PACKAGE TYPE

(A)

ZTZ = 697-pin plastic BGA, with Pb-Free solder balls

GTZ = 697-pin plastic BGA, with Pb-ed solder balls

DEVICE

A. BGA = Ball Grid Array

DEVICE SPEED RANGE

7 = 720 MHz

8 = 850 MHz

Blank = 1 GHz

( )

TEMPERATURE RANGE

Blank = 0°C to +90°C (default commercial temperature)

( )

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

TIdevicenomenclaturealsoincludesasuffixwiththedevicefamilyname.Thissuffixindicatesthe

packagetype(forexample,ZTZ),thetemperaturerange(forexample,blankisthedefaultcommercial

temperaturerange),andthedevicespeedrange,inmegahertz(forexample,blankis1000MHz[1GHz]).

Figure2-12providesalegendforreadingthecompletedevicenameforanyTMS320C64x+™DSP

generationmember.

FordevicepartnumbersandfurtherorderinginformationforTMS320C6454intheZTZ/GTZpackage

type,seetheTIwebsite(www.ti.com)orcontactyourTIsalesrepresentative.

Figure2-12.TMS320C64x+™DSPDeviceNomenclature(includingtheTMS320C6454DSP)

2.8.2.2DocumentationSupport

ThefollowingdocumentsdescribetheTMS320C6454Fixed-PointDigitalSignalProcessor.Copiesof

thesedocumentsareavailableontheInternetatwww.ti.com.Tip:Entertheliteraturenumberinthe

searchboxprovidedatwww.ti.com.

ThecurrentdocumentationthatdescribestheTMS320C6454,relatedperipherals,andothertechnical

collateral,isavailableintheC6000DSPproductfolderat:www.ti.com/c6000.

SPRU732TMS320C64x/C64x+DSPCPUandInstructionSetReferenceGuide.DescribestheCPU

architecture,pipeline,instructionset,andinterruptsfortheTMS320C64xandTMS320C64x+

digitalsignalprocessors(DSPs)oftheTMS320C6000DSPfamily.TheC64x/C64x+DSP

generationcomprisesfixed-pointdevicesintheC6000DSPplatform.TheC64x+DSPisan

enhancementoftheC64xDSPwithaddedfunctionalityandanexpandedinstructionset.

SPRU862TMS320C64x+DSPCacheUser'sGuide.Explainsthefundamentalsofmemorycaches

anddescribeshowthetwo-levelcache-basedinternalmemoryarchitectureinthe

TMS320C64x+digitalsignalprocessor(DSP)oftheTMS320C6000DSPfamilycanbe

efficientlyusedinDSPapplications.Showshowtomaintaincoherencewithexternal

memory,howtouseDMAtoreducememorylatencies,andhowtooptimizeyourcodeto

improvecacheefficiency.TheinternalmemoryarchitectureintheC64x+DSPisorganized

inatwo-levelhierarchyconsistingofadedicatedprogramcache(L1P)andadedicateddata

cache(L1D)onthefirstlevel.AccessesbytheCPUtothethesefirstlevelcachescan

completewithoutCPUpipelinestalls.IfthedatarequestedbytheCPUisnotcontainedin

cache,itisfetchedfromthenextlowermemorylevel,L2orexternalmemory.

SPRU871TMS320C64x+DSPMegamoduleReferenceGuide.DescribestheTMS320C64x+digital

signalprocessor(DSP)megamodule.Includedisadiscussionontheinternaldirectmemory

access(IDMA)controller,theinterruptcontroller,thepower-downcontroller,memory

protection,bandwidthmanagement,andthememoryandcache.

SPRAA84TMS320C64xtoTMS320C64x+CPUMigrationGuide.DescribesmigratingfromtheTexas

InstrumentsTMS320C64xdigitalsignalprocessor(DSP)totheTMS320C64x+DSP.The

DeviceOverview 48SubmitDocumentationFeedback