www.ti.com

PRODUCT PREVIEW

7.18IEEE1149.1JTAG

7.18.1JTAGDevice-SpecificInformation

7.18.2JTAGPeripheralRegisterDescription(s)

7.18.3JTAGElectricalData/Timing

TCK

TDO

TDI/TMS/TRST

1

2

3

4

2

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

7.18.1.1IEEE1149.1JTAGCompatibilityStatement

Formaximumreliability,theC6454DSPincludesaninternalpulldown(IPD)ontheTRSTpintoensure

thatTRSTwillalwaysbeasserteduponpowerupandtheDSP'sinternalemulationlogicwillalwaysbe

properlyinitializedwhenthispinisnotroutedout.JTAGcontrollersfromTexasInstrumentsactivelydrive

TRSThigh.However,somethird-partyJTAGcontrollersmaynotdriveTRSThighbutexpecttheuseof

anexternalpullupresistoronTRST.WhenusingthistypeofJTAGcontroller,assertTRSTtoinitializethe

DSPafterpowerupandexternallydriveTRSThighbeforeattemptinganyemulationorboundaryscan

operations.

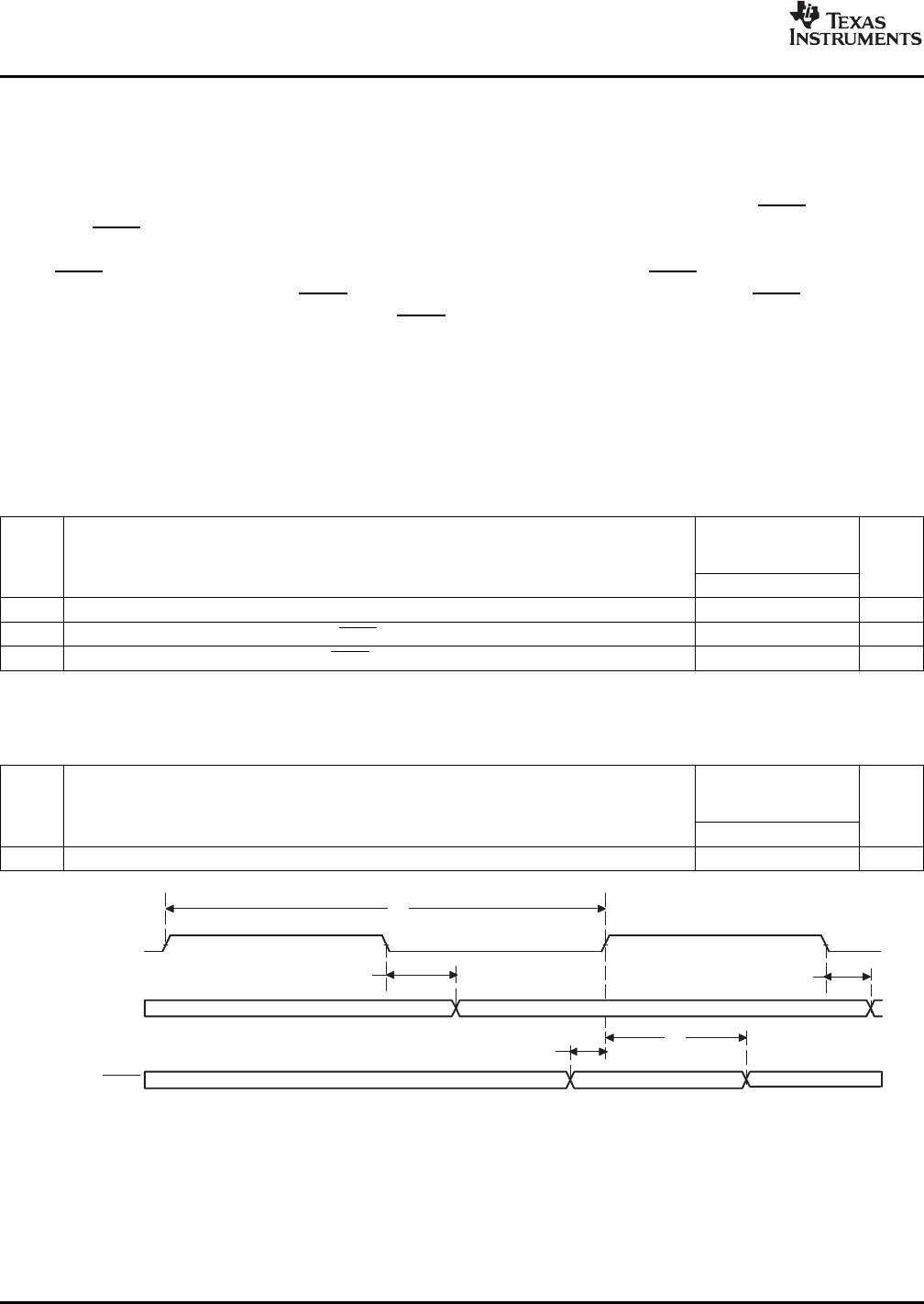

Table7-105.TimingRequirementsforJTAGTestPort(seeFigure7-75)

-720

-850

NO.UNIT

-1000

MINMAX

1t

c(TCK)

Cycletime,TCK35ns

3t

su(TDIV-TCKH)

Setuptime,TDI/TMS/TRSTvalidbeforeTCKhigh10ns

4t

h(TCKH-TDIV)

Holdtime,TDI/TMS/TRSTvalidafterTCKhigh9ns

Table7-106.SwitchingCharacteristicsOverRecommendedOperatingConditionsforJTAGTestPort

(seeFigure7-75)

-720

-850

NO.PARAMETERUNIT

-1000

MINMAX

2t

d(TCKL-TDOV)

Delaytime,TCKlowtoTDOvalid-318ns

Figure7-75.JTAGTest-PortTiming

216C64x+PeripheralInformationandElectricalSpecificationsSubmitDocumentationFeedback