www.ti.com

PRODUCT PREVIEW

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

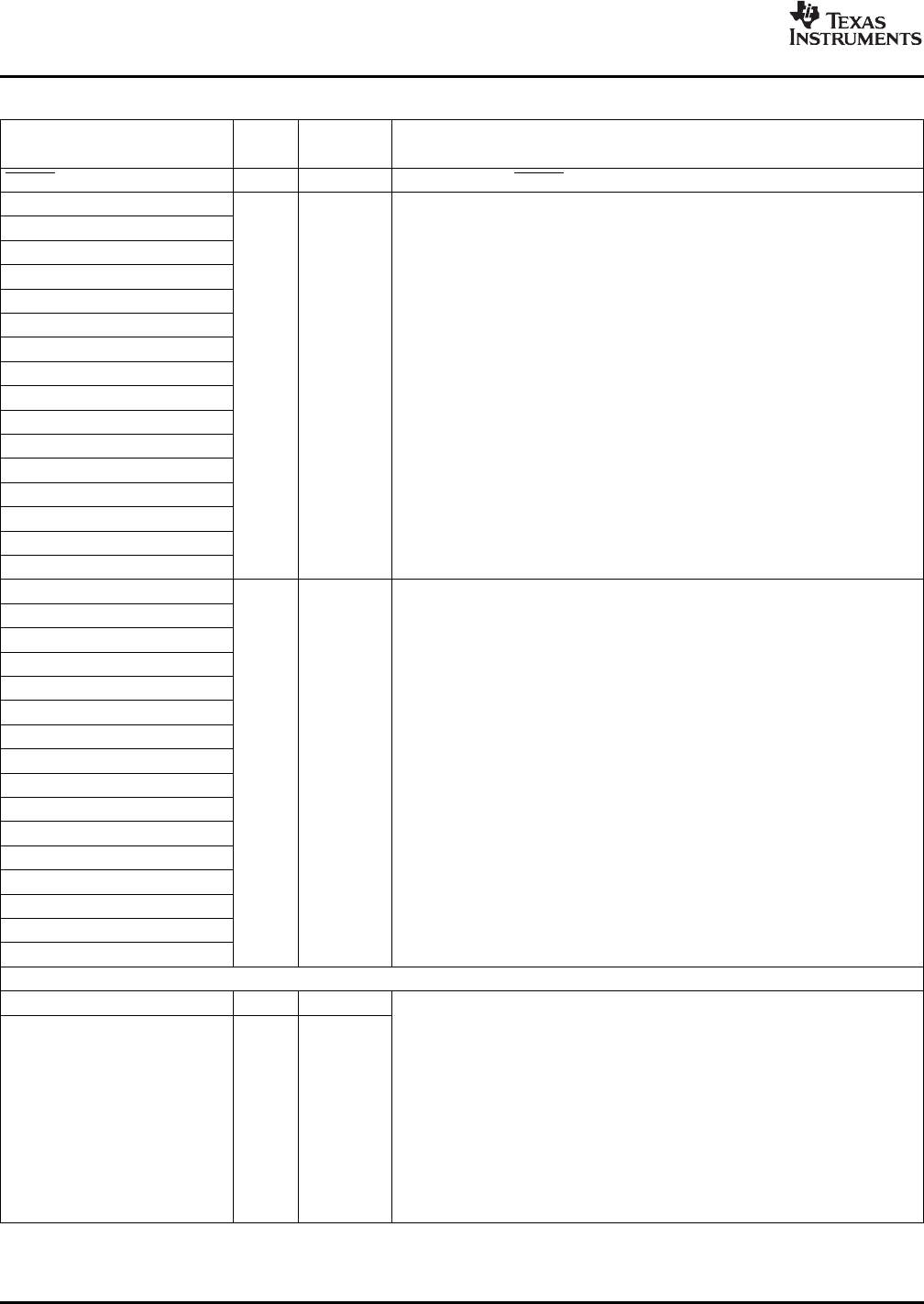

Table2-3.TerminalFunctions(continued)

SIGNAL

TYPE

(1)

IPD/IPU

(2)

DESCRIPTION

NAMENO.

PTRDYP4I/O/ZPCItargetready(PRTDY)(I/O/Z).Bydefault,thispinhasnofunction.

HD31/AD31AA3

HD30/AD30AA5

HD29/AD29AC4

HD28/AD28AA4

HD27/AD27AC5

HD26/AD26Y1

HD25/AD25AD2

HD24/AD24W1

Host-portdata[31:16]pin(I/O/Z)[default]orPCIdata-addressbus[31:16]

I/O/Z

(I/O/Z)

HD23/AD23AC3

HD22/AD22AE1

HD21/AD21AD1

HD20/AD20W2

HD19/AD19AC1

HD18/AD18Y2

HD17/AD17AB1

HD16/AD16Y3

HD15/AD15AB2

HD14/AD14W4

HD13/AD13AC2

HD12/AD12V4

HD11/AD11AF3

HD10/AD10AE3

HD9/AD9AB3

HD8/AD8W5

I/O/ZHost-portdata[15:0]pin(I/O/Z)[default]orPCIdata-addressbus[15:0](I/O/Z)

HD7/AD7AB4

HD6/AD6Y4

HD5/AD5AD3

HD4/AD4Y5

HD3/AD3AD4

HD2/AD2W6

HD1/AD1AB5

HD0/AD0AE2

EMIFA(64-BIT)-CONTROLSIGNALSCOMMONTOALLTYPESOFMEMORY

ABA1/EMIFA_ENV25O/ZIPDEMIFAbankaddresscontrol(ABA[1:0])

•Active-lowbankselectsforthe64-bitEMIFA.

Wheninterfacingto16-bitAsynchronousdevices,ABA1carriesbit1ofthe

byteaddress.

Foran8-bitAsynchronousinterface,ABA[1:0]areusedtocarrybits1and

0ofthebyteaddress

DDR2MemoryControllerenable(DDR2_EN)[ABA0]

ABA0/DDR2_ENV26O/ZIPD

0-DDR2MemoryControllerperipheralpinsaredisabled(default)

1-DDR2MemoryControllerperipheralpinsareenabled

EMIFAenable(EMIFA_EN)[ABA1]

0-EMIFAperipheralpinsaredisabled(default)

1-EMIFAperipheralpinsareenabled

DeviceOverview 26SubmitDocumentationFeedback