www.ti.com

PRODUCT PREVIEW

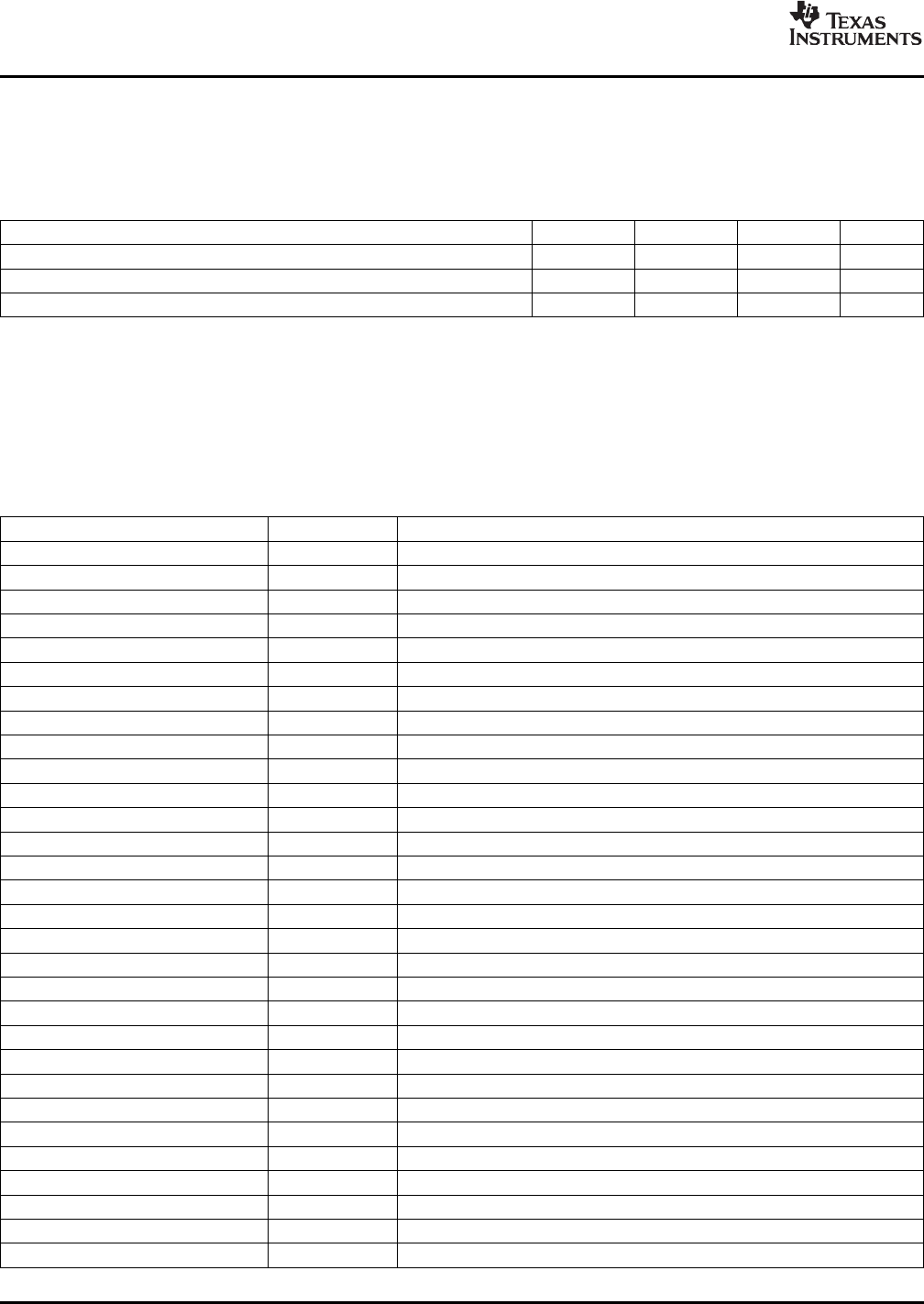

7.7.2PLL1ControllerMemoryMap

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

ThePLLlocktimeistheamountoftimeneededfromwhenthePLListakenoutofreset(PLLRST=1

withPLLEN=0)towhentowhenthePLLcontrollercanbeswitchedtoPLLmode(PLLEN=1).The

PLL1locktimeisgiveninTable7-17.

Table7-17.PLL1Stabilization,Lock,andResetTimes

MINTYPMAXUNIT

PLLstabilizationtime150µs

PLLlocktime2000*C

(1)

ns

PLLresettime128*C

(1)

ns

(1)C=CLKIN1cycletimeinns.Forexample,whenCLKIN1frequencyis50MHz,useC=20ns.

ThememorymapofthePLL1controllerisshowninTable7-18.Notethatonlyregistersdocumentedhere

areaccessibleontheTMS320C6454.OtheraddressesinthePLL1controllermemorymapshouldnotbe

modified.

Table7-18.PLL1ControllerRegisters(IncludingResetController)

HEXADDRESSRANGEACRONYMREGISTERNAME

029A0000-029A00E3-Reserved

029A00E4RSTYPEResetTypeStatusRegister(ResetController)

029A00E8-029A00FF-Reserved

029A0100PLLCTLPLLControlRegister

029A0104-Reserved

029A0108-Reserved

029A010C-Reserved

029A0110PLLMPLLMultiplierControlRegister

029A0114PREDIVPLLPre-DividerControlRegister

029A0118-Reserved

029A011C-Reserved

029A0120-Reserved

029A0124-Reserved

029A0128-Reserved

029A012C-Reserved

029A0130-Reserved

029A0134-Reserved

029A0138PLLCMDPLLControllerCommandRegister

029A013CPLLSTATPLLControllerStatusRegister

029A0140ALNCTLPLLControllerClockAlignControlRegister

029A0144DCHANGEPLLDIVRatioChangeStatusRegister

029A0148-Reserved

029A014C-Reserved

029A0150SYSTATSYSCLKStatusRegister

029A0154-Reserved

029A0158-Reserved

029A015C-Reserved

029A0160PLLDIV4PLLControllerDivider4Register

029A0164PLLDIV5PLLControllerDivider5Register

029A0168-029BFFFF-Reserved

C64x+PeripheralInformationandElectricalSpecifications 126SubmitDocumentationFeedback