www.ti.com

PRODUCT PREVIEW

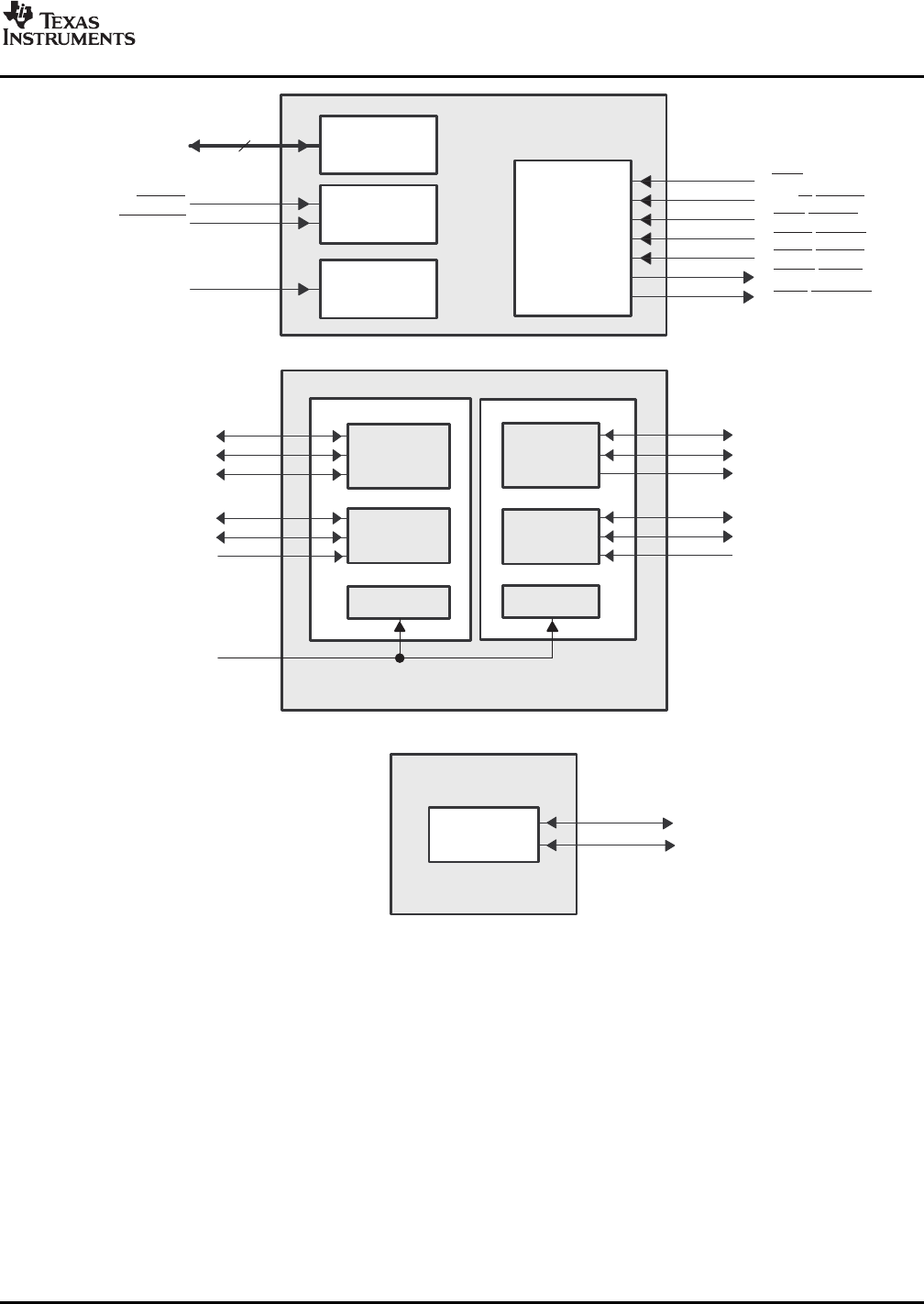

McBSPs

(Multichannel Buffered Serial Ports)

(B)

CLKX0

FSX0

DX0

CLKR0

FSR0

DR0

Transmit

McBSP0

Receive

Clock

CLKX1/GP[3]

FSX1/GP[11]

DX1/GP[9]

CLKR1/GP[0]

FSR1/GP[10]

DR1/GP[8]

Transmit

McBSP1

Receive

Clock

HHWIL/PCLK

HCNTL0/PSTOP

HCNTL1/PDEVSEL

Data

Register Select

Half-Word

Select

Control

HPI

(A)

(Host-Port Interface)

32

HAS/PPAR

HR/W/PCBE2

HCS/PPERR

HDS1/PSERR

HDS2/PCBE1

HRDY/PIRDY

HINT/PFRAME

(HPI16 ONLY)

HD[15:0]/AD[15:0]

HD[31:16]/AD[31:16]

SCL

I2C

SDA

A. These HPI pins are muxed with the PCI peripheral. By default, these pins function as HPI. When the HPI is enabled, the number of HPI pins

used depends on the HPI configuration (HPI16 or HPI32). For more details on these muxed pins, see the Device Configuration section of this

document.

B. These McBSP1 peripheral pins are muxed with the GPIO peripheral pins and by default these signals function as GPIO peripheral pins. For

more details, see the Device Configuration section of this document.

CLKS

(SHARED)

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

Figure2-9.HPI/McBSP/I2CPeripheralSignals

SubmitDocumentationFeedbackDeviceOverview21