www.ti.com

PRODUCT PREVIEW

1

0

0 1

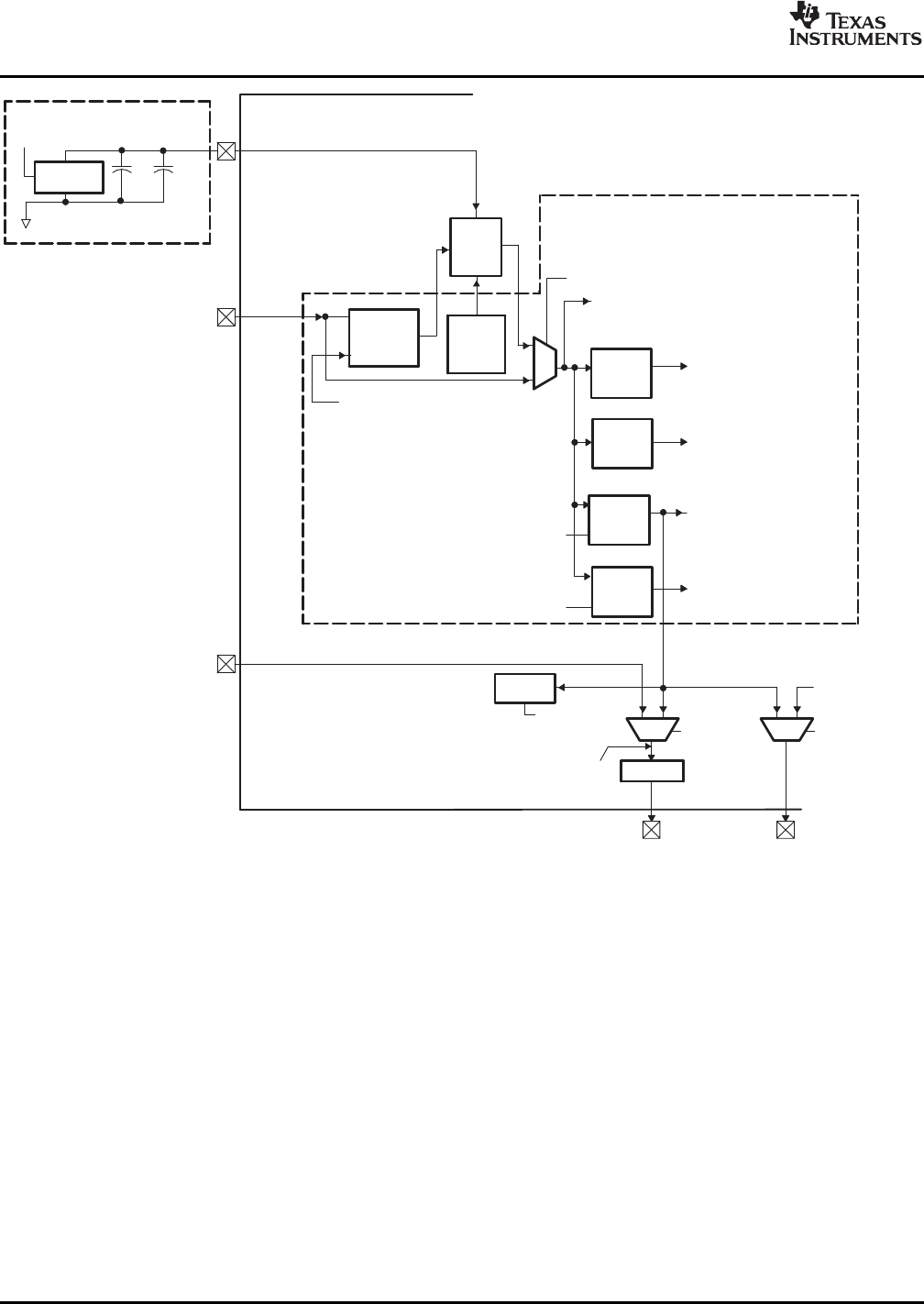

DIVIDER D4

CLKIN1

(B)

PLLEN (PLLCTL.[0])

SYSCLK2

SYSCLK3

AECLKIN (External EMIF Clock Input)

EMIFA

DIVIDER PREDIV

DIVIDER D2

(A)

DIVIDER D3

(A)

AECLKOUT

PLLV1

C2

C1

EMI Filter

+1.8 V

560 pF 0.1 mF

SYSCLK5

(Emulation and Trace)

SYSREFCLK

(C64x+ MegaModule)

AECLKINSEL

(AEA[15] pin)

DIVIDER D5

PLL1 Controller

(EMIF Input Clock)

TMS320C6454 DSP

/1, /2, /3

ENA

PREDEN (PREDIV.[15])

/3

/6

ENA

/2, /4,

..., /16

ENA

PLL1

PLLM

x1, x15,

x20, x25,

x30, x32

D4EN (PLLDIV4.[15])

D5EN (PLLDIV4.[15])

SYSCLK4

(Internal EMIF Clock Input)

/1, /2,

..., /8

1 0

GP1/SYSCLK4

SYSCLKOUT_EN

(AEA[4] pin)

GP0

/1, /2,

..., /8

CLKDIV

(CTRL.[18:16])

PLLOUT

PLLREF

7.7.1PLL1ControllerDevice-SpecificInformation

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

A.DIVIDERD2andDIVIDERD3arealwaysenabled.

B.CLKIN1isa3.3-Vsignal.

Figure7-10.PLL1andPLL1Controller

7.7.1.1InternalClocksandMaximumOperatingFrequencies

AsshowninFigure7-10,thePLL1controllergeneratesseveralinternalclocksincludingthesystem

referenceclock(SYSREFCLK),andthesystemclocks(SYSCLK2/3/4/5).Thehigh-frequencyclocksignal

SYSREFCLKisdirectlyusedtoclocktheC64x+megamodule(includingtheCPU)andalsoservesasa

referenceclockfortherestoftheDSPsystem.

DividersD2,D3,D4,andD5dividethehigh-frequencyclockSYSREFCLKtogenerateSYSCLK2,

SYSCLK3,SYSCLK4,andSYSCLK5,respectively.Thesystemclocksareusedtoclockdifferentportions

oftheDSP:

•SYSCLK2isusedtoclocktheswitchedcentralresources(SCRs),EDMA3,aswellasthedatabus

interfacesoftheEMIFAandDDR2MemoryController.

•SYSCLK3clocksthePCI,HPI,McBSP,GPIO,TIMER,andI2Cperipherals,aswellasthe

configurationbusofthePLL2Controller.

C64x+PeripheralInformationandElectricalSpecifications 124SubmitDocumentationFeedback