www.ti.com

PRODUCT PREVIEW

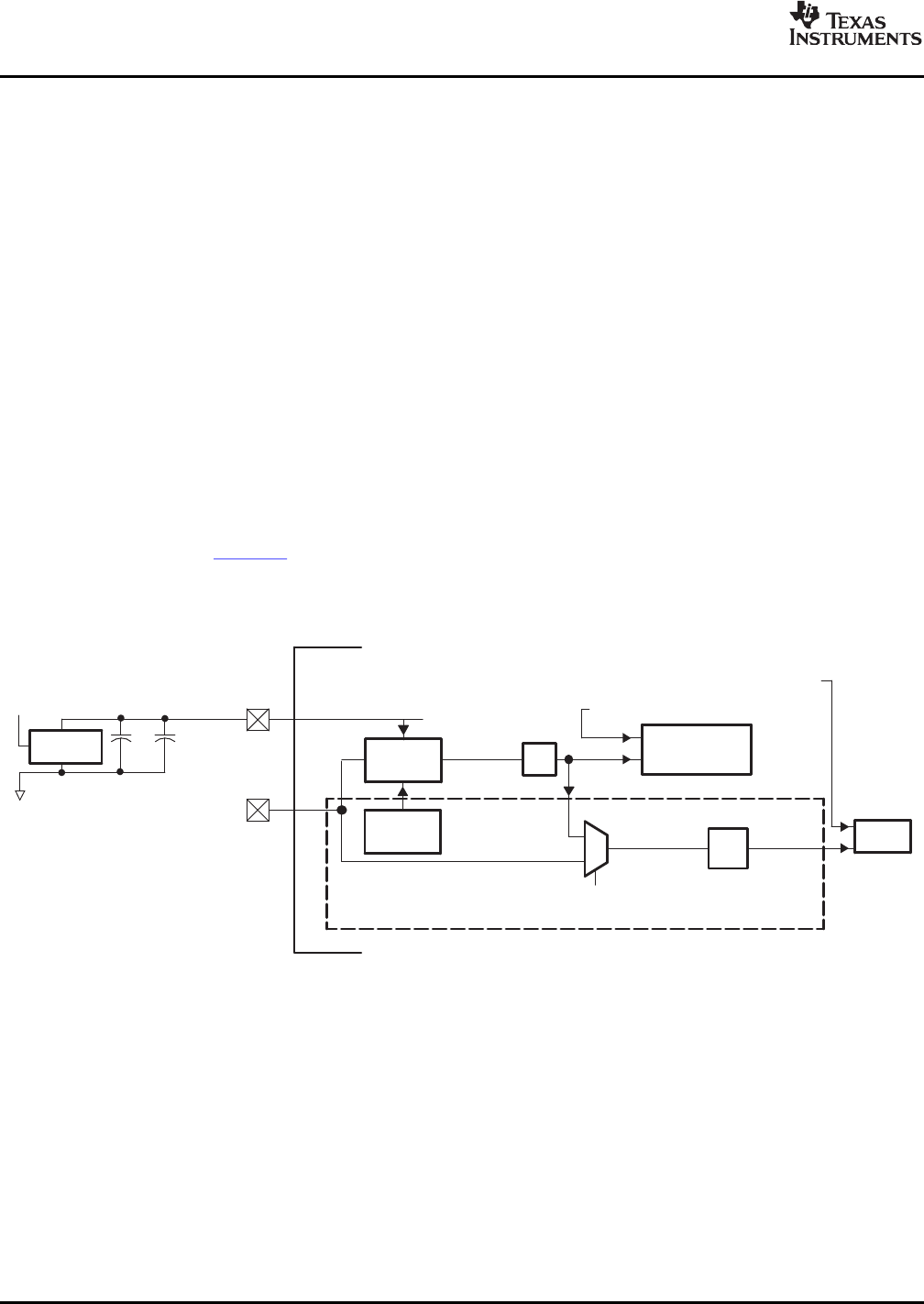

7.8PLL2andPLL2Controller

PLLV2

PLL2

SYSCLK2 (From PLL1 Controller)

SYSCLK1

DDR2

Memory

Controller

EMAC

CLKIN2

(B)(C)

C162

560 pF

EMI Filter

+1.8 V

C161

0.1 pF

PLL2 Controller

TMS320C6454 DSP

PLLM

x20

/2

1

0

/x

(A)

1

SYSREFCLK

SYSCLK3 (From PLL1 Controller)

PLLREF PLLOUT

DIVIDER D1

TMS320C6454

Fixed-PointDigitalSignalProcessor

SPRS311A–APRIL2006–REVISEDDECEMBER2006

ThesecondaryPLLcontrollergeneratesinterfaceclocksfortheEthernetmediaaccesscontroller(EMAC)

andtheDDR2memorycontroller.

AsshowninFigure7-23,thePLL2controllerfeaturesaPLLmultipliercontrollerandonedivider(D1).The

PLLmultiplierisfixedtoax20multiplierrateandthedividerD1canbeprogrammedtoa÷2or÷5mode.

PLL2powerissuppliedexternallyviathePLL2powersupply(PLLV2).AnexternalPLLfiltercircuitmust

beaddedtoPLLV2asshowninFigure7-23.The1.8-VsupplyfortheEMIfiltermustbefromthesame

1.8-VpowerplanesupplyingtheI/Opower-supplypin,DV

DD18

.TIrequiresEMIfiltermanufacturerMurata,

partnumberNFM18CC222R1C3.

AllPLLexternalcomponents(C161,C162,andtheEMIFilter)shouldbeplacedasclosetotheC64x+

DSPdeviceaspossible.Forthebestperformance,TIrequiresthatallthePLLexternalcomponentsbeon

asinglesideoftheboardwithoutjumpers,switches,orcomponentsotherthantheonesshown.For

reducedPLLjitter,maximizethespacingbetweenswitchingsignalsandthePLLexternalcomponents

(C161,C162,andtheEMIFilter).TheminimumCLKIN2riseandfalltimesshouldalsobeobserved.For

theinputclocktimingrequirements,seeSection7.8.4,PLL2ControllerInputClockElectricalData/Timing.

CAUTION

ThePLLcontrollermoduleasdescribedintheTMS320C645xDSP

Software-ProgrammablePhase-LockedLoop(PLL)ControllerUser'sGuide(literature

numberSPRUE56)includesasupersetoffeatures,someofwhicharenotsupported

ontheC6454DSP.Thefollowingsectionsdescribethefeaturesthataresupported;it

shouldbeassumedthatanyfeaturenotincludedinthesesectionsisnotsupported

bytheC6454DSP.

A./xmustbeprogrammedto/2forGMII(default)andto/5forRGMII.

B.IfEMACisenabledwithRGMII,orGMII,CLKIN2frequencymustbe25MHz.

C.CLKIN2isa3.3-Vsignal.

Figure7-23.PLL2BlockDiagram

138C64x+PeripheralInformationandElectricalSpecificationsSubmitDocumentationFeedback