Monitor: Basic Operation

10006024-04 Katana®752i User’s Manual

15-5

Power-Up Timing

Upon power-up, the Katana®752i initially retries cPCI cycles for a specific period of time

(see “cPCI/PCI Stop Retries, Memory Read Access Only” monitor state in the tables below).

After that time, it stops retrying cycles on the cPCI bus.

Caution: Any read access between the “cPCI/PCI Stop Retries, Memory Read Access Only” and “Final

Memory Initialization” monitor states (see

Table 15-1 and Table 15-2) may result in an ECC

exception on the Katana®752i.

The following tables show the monitor power-up timing for booting from both socked and

soldered flash memory.

Note: The resolution for the measured times in Table 15-1 and Table 15-2 is ±10 milliseconds. The measurements

were performed from a front panel reset. The Katana®752i used in these tests had 512 megabytes of RAM

with ECC and Clear Memory On. CompactPCI mode was also enabled.

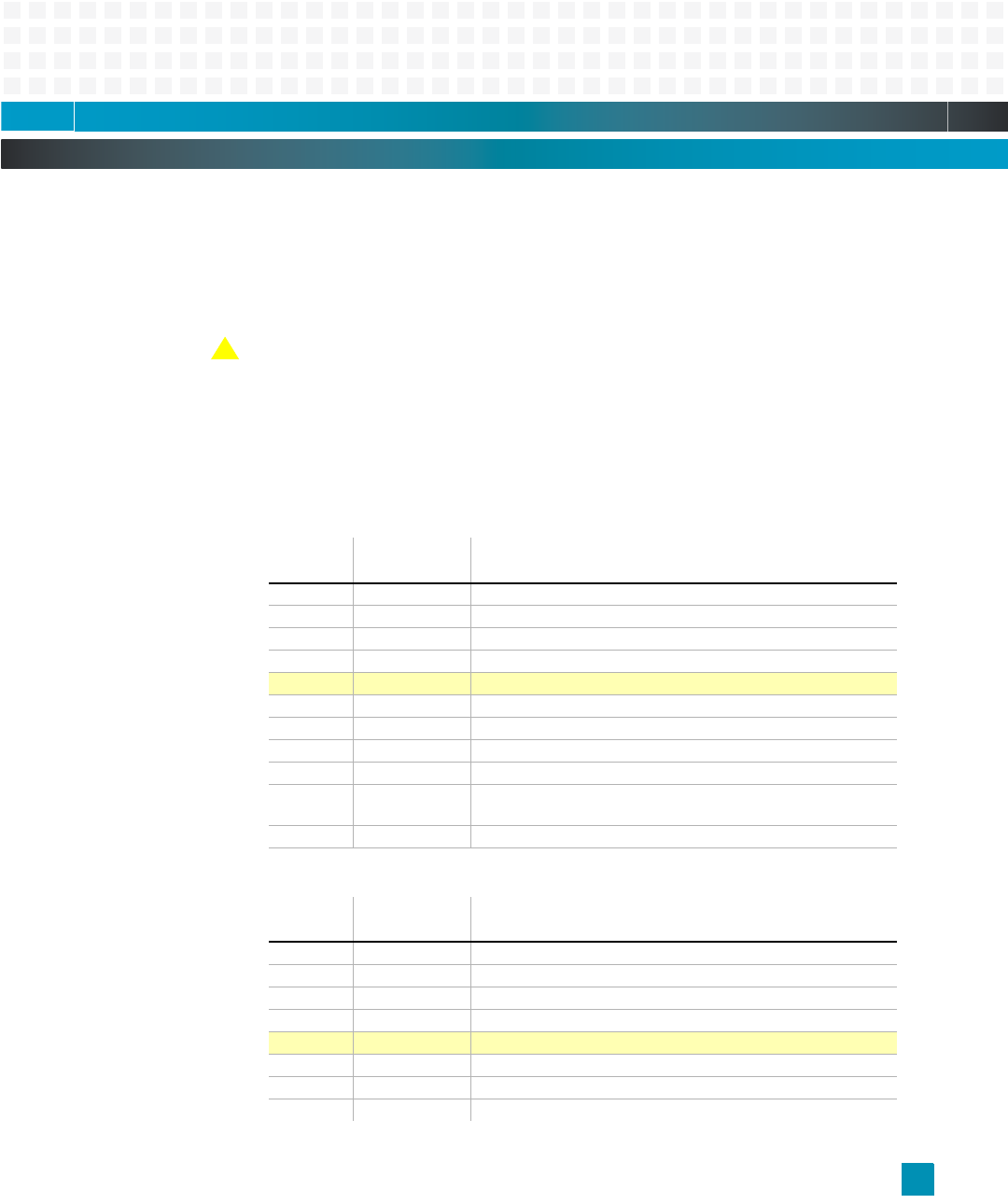

Table 15-1: Power-Up Timing for Booting from Soldered Flash

Table 15-2: Power-Up Timing for Booting from Socketed Flash

Time

(sec):

Debug LED

State (bits): Monitor State:

0 n/a System Reset

0.157 0001 CPU and MV64460 Setup

0.200 0010 Early I

2

C Setup, cPCI mode only

0.216 0011 Early Memory Initialization, ECC Off

0.221 0100 cPCI/PCI Stop Retries, Memory Read Access Only

0.490 0101 Serial Port Initialized

0.623 0110 Display CPU, Board and Bus Speed Information

2.563 0111 Final Memory Initialization, ECC and Clear

2.857 1000 Monitor code relocated to top of memory

4.627 1001 PCI/cPCI Final Setup. Enumeration. Memory Read/Write Access

available through PCI/cPCI

4.915 0000 Monitor Prompt

Time

(sec):

Debug LED

State (bits): Monitor State:

0 n/a System Reset

0.159 0001 CPU and MV64460 Setup

0.250 0010 Early I

2

C Setup, cPCI mode only

0.282 0011 Early Memory Initialization, ECC Off

0.293 0100 cPCI/PCI Stop Retries, Memory Read Access Only

0.817 0101 Serial Port Initialized

0.978 0110 Display CPU, Board and Bus Speed Information

4.864 0111 Final Memory Initialization, ECC and Clear

!