System Controller: GPIO Signal Definitions

Katana

®

752i User’s Manual 10006024-04

5-10

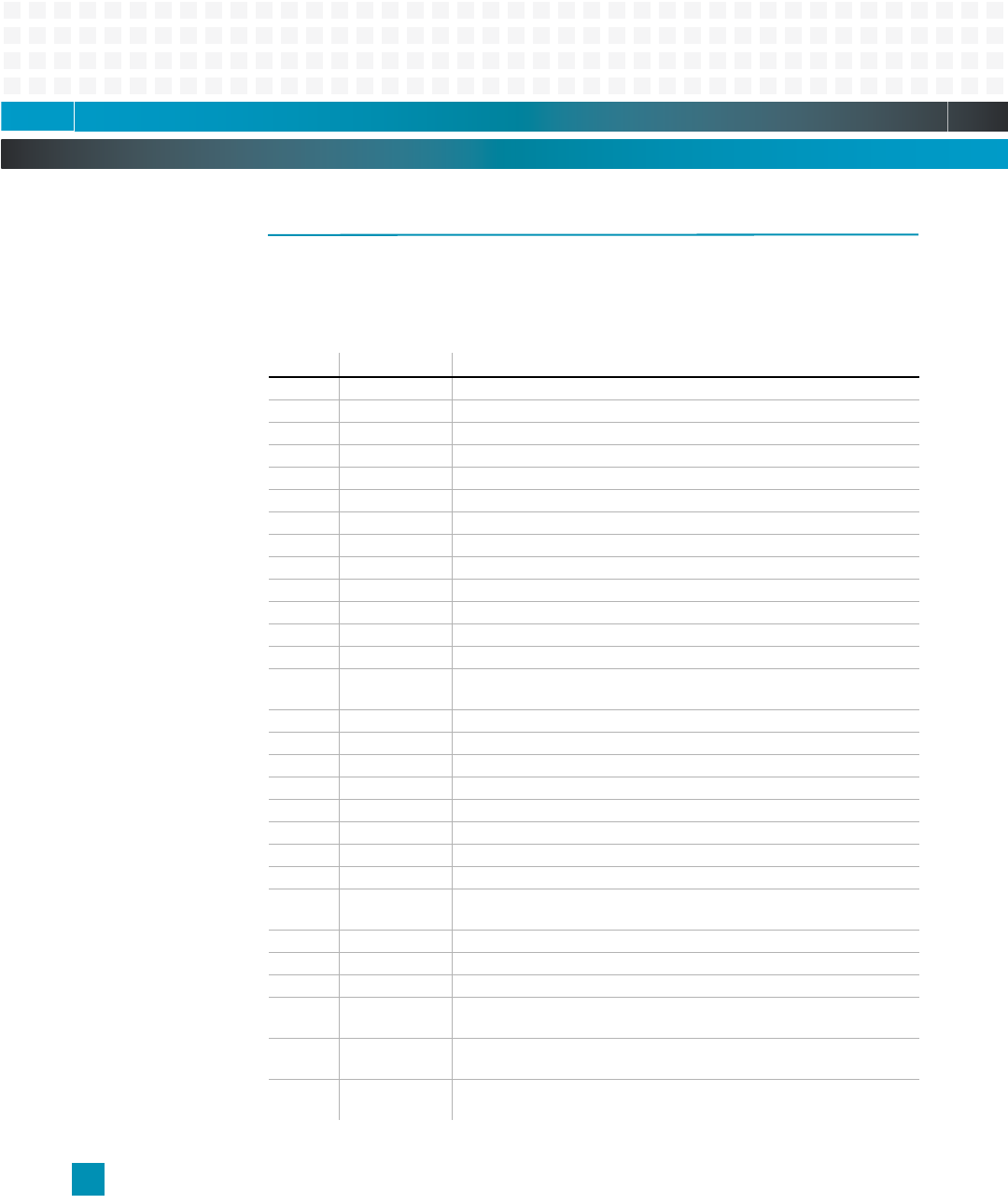

GPIO SIGNAL DEFINITIONS

The MV64460 system controller on the Katana

®

752i has 32 general-purpose input output

(GPIO) pins that are used for various purposes. The following table describes the GPIO pin

assignments.

Table 5-3: GPIO Signals Definitions

Pin: Direction: Description:

0 output console port transmit data

1 input console port receive data

2output PTMC site #1 PCI grant

3 input PTMC site #1 PCI request

4output PTMC site #2 PCI grant

5 input PTMC site #2 PCI request

6 output Ethernet MAC PCI grant

7 input Ethernet MAC PCI request

8 input PCI1 INTA

9 input PCI1 INTB

10 input PCI1 INTC

11 output INIT_ACT, driven to indicate the bridge is loading from serial ROM

12 input input from CPLD, used as synchronous versions of PERR and SERR

13 output driven low to turn off front panel fault LED once processor section is up

and running

14 input PCI1 INTD

15 – unused

16 output watchdog NMI

17 output watchdog expired

18 output I2C_HOLDOFF signal (Zircon PM)

19 output output enable for PTMC RMII clocks

20 input baud rate input clock for serial port

21—22 – unused

23 input IPMI Timerout, driven by IPMI microcontroller when there is a time-

out condition

24 output POST indicator

25 output driven high to put the IPMI microcontroller in reset

26 input Watchdog Maskable Interrupt (in)

27 input GIG0_INT interrupt signal from gigabit PHY (unused on rev. 0—1

boards)

28 input GIG1_INT interrupt signal from gigabit PHY (unused on rev. 0—1

boards)

29 input GIG2_INT interrupt signal from gigabit PHY (unused on rev. 0—1

boards)