Processor: Processor Initialization

10006024-04 Katana

®

752i User’s Manual

4-5

Hardware Implementation Dependent 0 Register

The Hardware Implementation Dependent 0 Register (HID0) contains bits for CPU-specific

features. Most of these bits are cleared on initial power-up of the Katana

®

752i. Please refer

to the IBM PowerPC documentation for more detailed descriptions of the HIDx registers.

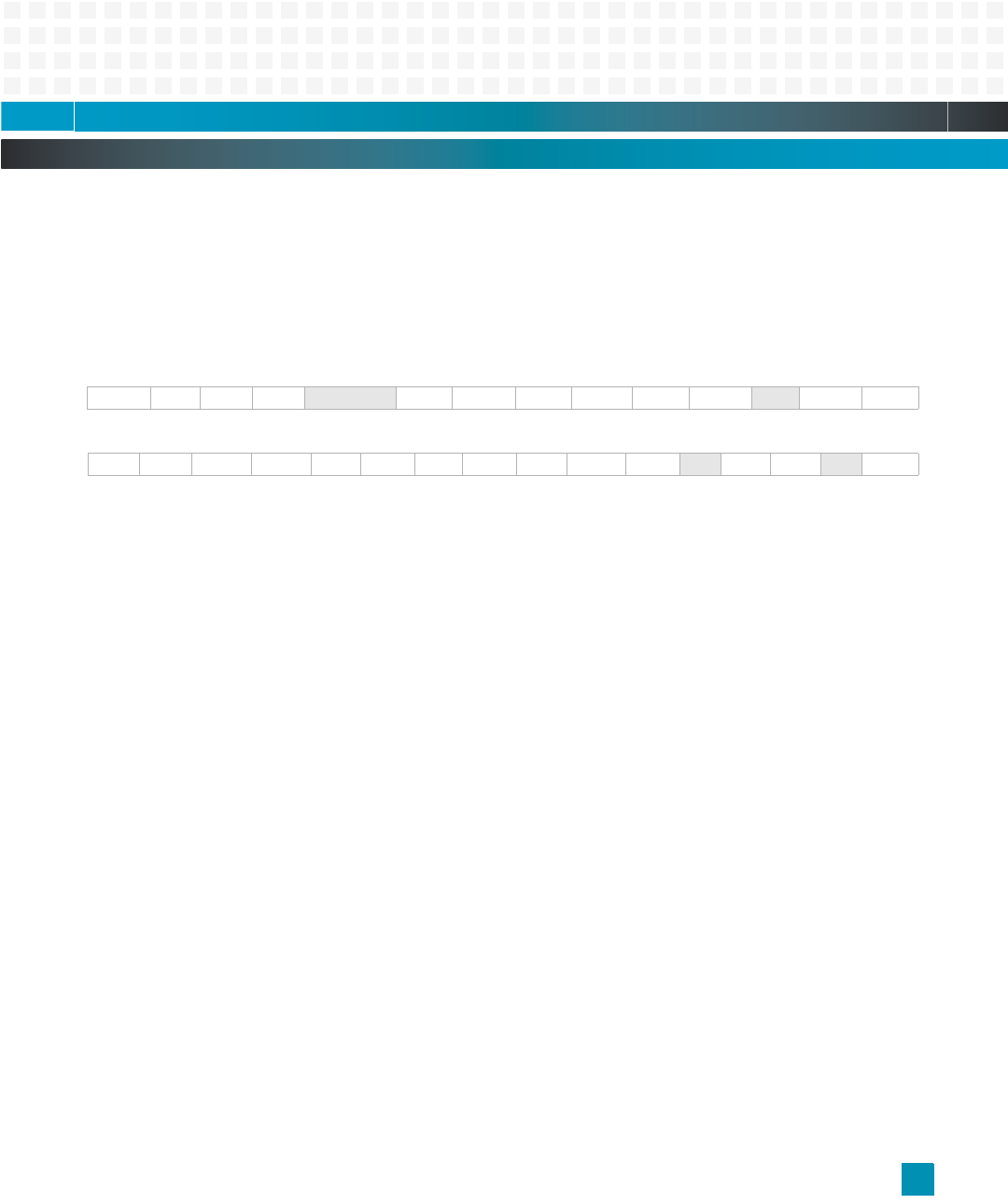

The following register map summarizes HID0 for the 750GL CPU:

Register 4-1: 750GL Hardware Implementation Dependent, HID0

EMCP: Enable Machine Check Pin. Initially enabled on the Katana

®

752i.

DBP: Disable 60x Bus address and data Parity generation (in conjunction with EBA/EBD).

EBA: Enable 60x Bus Address parity checking.

EBD: Enable 60x Bus Data parity checking.

PAR: Disable Precharge of ARTRY* and shared signals.

DOZE: Select low-power doze.

NAP: Select low-power nap.

SLEEP: Select low-power sleep.

DPM: Enable Dynamic Power Management.

RISEG: Read Instruction Segment Register (test only).

NHR: Not Hard Reset (software use only).

MUM: Miss-Under-Miss Enable.

ICE/DCE: Instruction and Data Cache Enables.

I/DLOCK: Instruction and Data Cache Lock bits.

ICFI/DCFI: Instruction and Data Cache Flash Invalidate bits.

SPD: DCache and ICache Speculative access disable.

IFEM: Enable M bit on bus for Instruction Fetches.

SGE: Store Gathering Enable.

DCFA: Data Cache Flush Assist.

Force data cache to ignore invalid sets on miss replacement selection.

0 1 2 34 67 8 9 1011 121314 15

EMCP DBP EBA EBD Reserved PAR DOZE NAP

SLEEP

DPM RISEG

Res.

MUM NHR

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

ICE DCE

ILOCK

DLOCK

ICFI DCFI

SPD IFEM

SGE DCFA BTIC

Res

ABE BHT

Res

NOOPTI