System Controller: I2C Interface

Katana

®

752i User’s Manual 10006024-04

5-8

EEPROMs

The MV64460 uses an 8-kilobyte serial EEPROM at hex location 53

16

on the I

2

C bus to store

configuration data. Also, the MV64460 provides a second 8-kilobyte serial EEPROM at hex

location A6

16

on the I

2

C bus to provide additional non-volatile information such as board,

monitor, and operating system configurations. All Emerson-specific data is stored in the

upper 2 kilobytes of the device. The SROM data organization is allocated as follows.

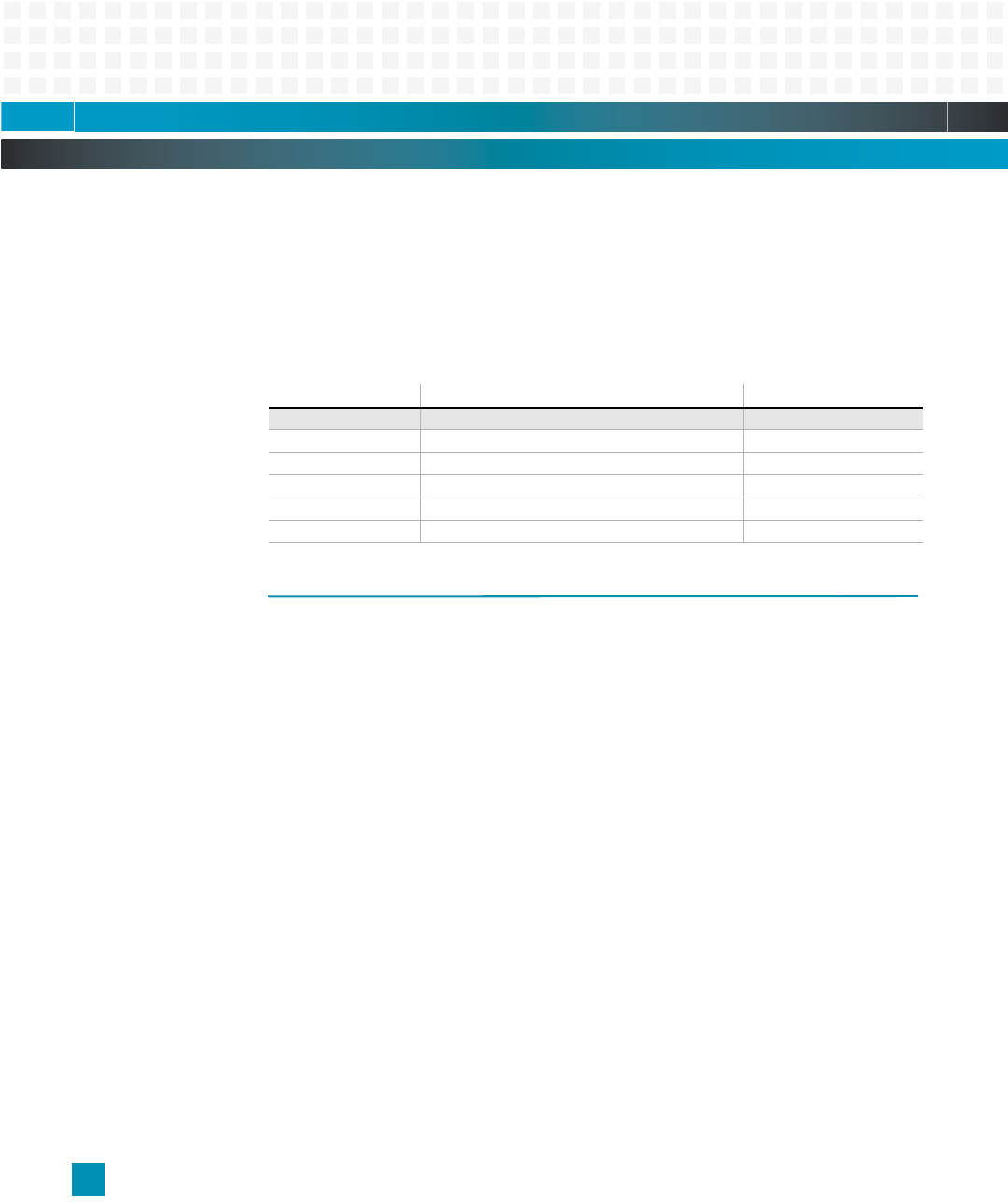

Table 5-2: NVRAM Allocation

I

2

C INTERFACE

The MV64460 has a built-in inter-integrated circuit (I

2

C) interface that supports master and

slave I

2

C devices. The following devices connect to the I

2

C bus:

• SO-DIMM SDRAM

• two 64-kilobit serial EEPROMs

• real-time clock (RTC) device

• Zircon PM IPMI controller and associated devices

The multiplexer shown in

Fig. 5-2 actually consists of two switches. One switch allows the

750GL processor to access the IPMI serial ROMs only while the IPMI controller is held in

reset. The second switch allows the 750GL processor to access I

2

C Port #1 only while back-

end power is up–otherwise this connection is isolated. (Please refer to the Katana

®

752i

schematics for details.)

Address Offset: Name: Window Size:

0x1E00-0x1FFF Reserved 0x0200 (512) bytes

0x1DDC-0x1DFF BootVerify parameters 0x0024 (36) bytes

0x1DD8-0x1DDB Power-on self-test (POST) diagnostic results 0x0004 (4) bytes

0x1800-0x1DD7 Monitor configuration parameters 0x05D8 (1496) bytes

0x1600-0x17FF Operating system 0x0200 (512) bytes

0x0000-0x15FF User Defined 0x1600 (5632) bytes