Processor: Cache Memory

10006024-04 Katana

®

752i User’s Manual

4-11

CACHE MEMORY

The 750GL processor provides both level 1 (L1) and level 2 (L2) cache memory. This section

describes this memory.

L1 Cache

The 750GL processor has separate, on-chip, 32-kilobyte, Level 1 (L1) instruction and data

caches with eight-way, set-associative translation lookaside buffers (TLBs). The CPU sup-

ports the modified/exclusive/invalid (MEI) cache coherency protocol. The data bus width

for bus interface unit (BIU) accesses of the L1 data cache array is 256 bits. This enables

cache line data burst to be read from or written to the cache array in a single cycle, reducing

cache contention between the BIU and the load-store unit. The 750GL also employs

pseudo-least recently used (PLRU) replacement algorithms for enhanced performance.

L2 Cache

The internal L2 cache is four-way set associative. Each way contains 4096 blocks, and each

block consists of two 32-byte sectors. It can be configured with any combination of individ-

ual ways locked. It can lock half or all of the ways, or it can unlock them all. When unlocked,

the L2 cache is four-way set associative. Each way contains 262144 blocks, and each block

consists of two 32-byte sectors.

The L2 cache can be configured to contain instructions or data only. Array read and write

operations execute in one processor cycle—writes are 64 bits wide and reads are 256 bits

wide. The L2 has a 1MB SRAM which includes an 8-bit ECC for every 64-bit word in memory

that can be used to correct most single bit errors and detect multiple bit errors.

The L2 cache control register (L2CR) configures and enables the L2 cache. The L2CR is

read/write and contents are cleared during power-on reset.

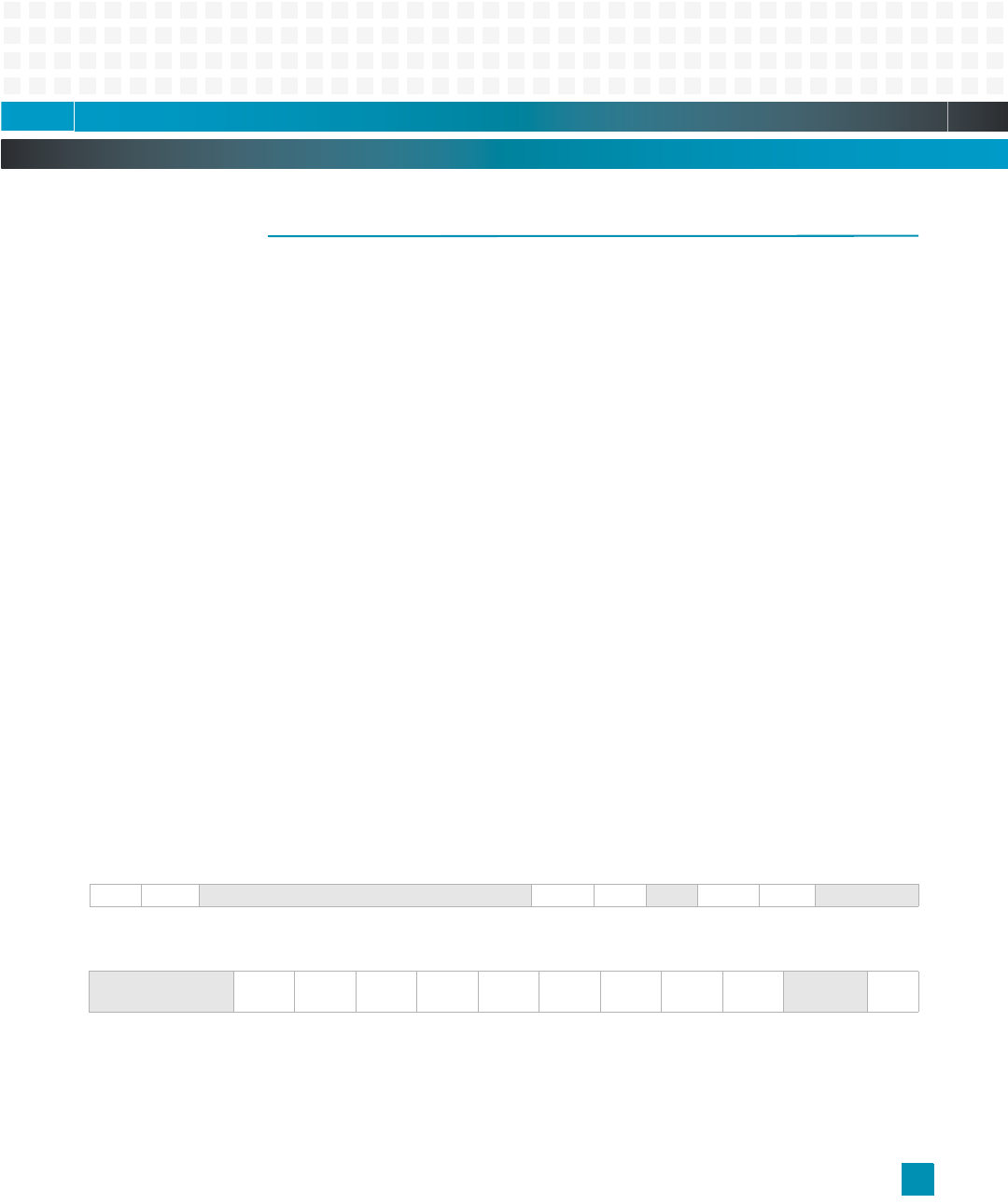

Register 4-5: L2 Cache Control Register (L2CR)

L2E: L2 Enable.

Enables and disables the operation of the L2 cache, starting with the next transaction.

L2CE: L2 double bit error Checkstop Enable.

0 1 2 8 9 1011 12 131415

L2E L2CE Reserved L2DO L2I Res. L2WT L2TS Reserved

16

1

9202122232425262728293031

Reserved

L2

L0CK LO

L2

LOCK HI

SHEE

SHERR

L2

LOCK0

L2

LOCK1

L2

LOCK2

L2

LOCK3

L2IO Reserved L2IP