System Controller: PCI Interface

10006024-04 Katana

®

752i User’s Manual

5-5

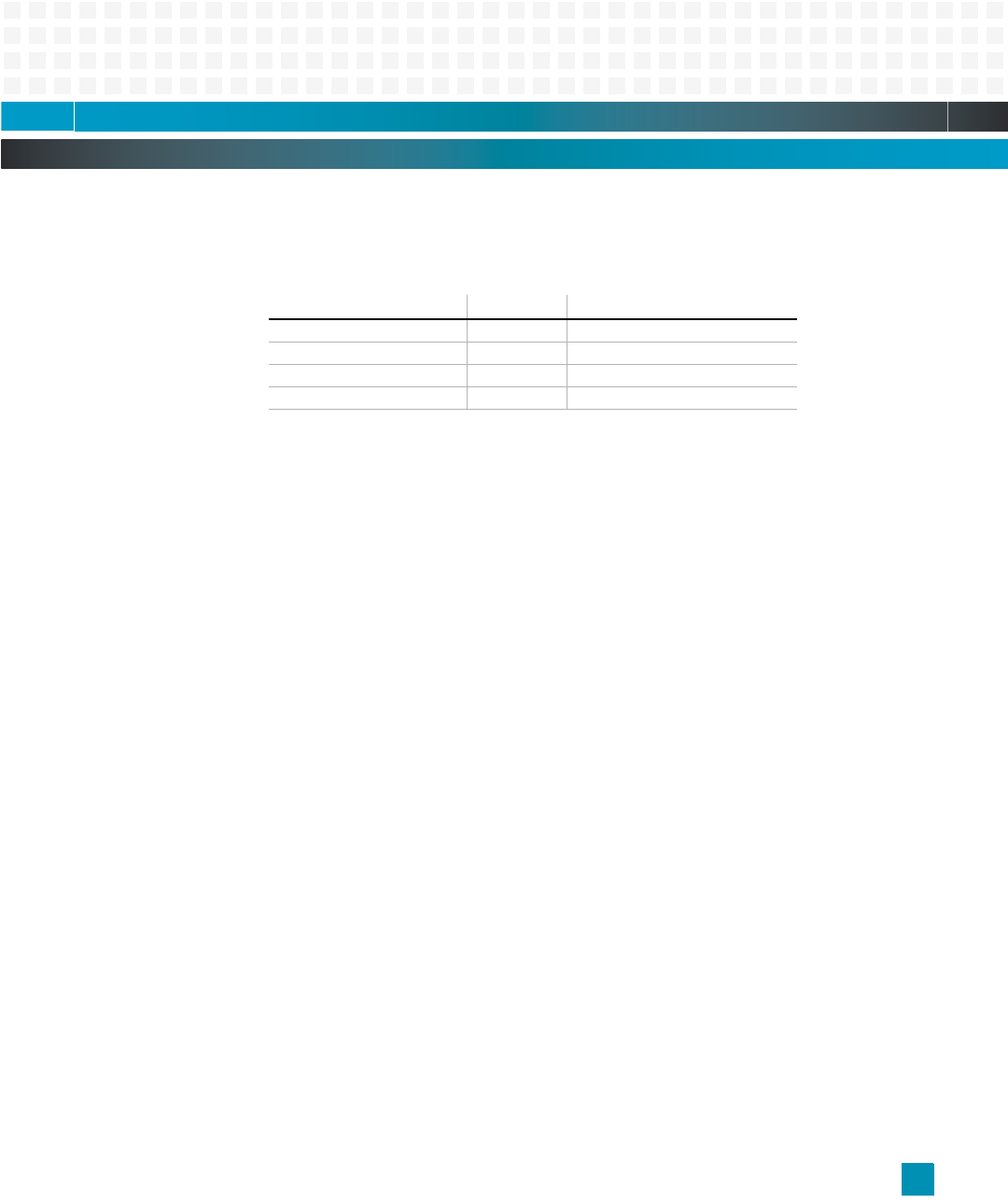

PCI Identification

The Katana

®

752i has been assigned the following PCI identification numbers.

Table 5-1: PCI Identification Values

PCI Read/Write

The MV64460 becomes a PCI bus master when the CPU, IDMA, or MPSC SDMAs initiate a

bus cycle to a PCI device. Conventional PCI mode allows unlimited DMA bursts between PCI

and memory. It supports all PCI commands including 64-bit addressing using dual access

cycles (DAC).

The MV64460 acts as a target when a PCI device initiates a memory access (or an I/O access

in the case of internal registers, or a P2P transaction). It responds to all memory read and

write accesses, including DAC, and to all configuration and I/O cycles in the case of internal

registers. Its internal buffers allow unlimited burst reads and writes, and they support up to

four pending delayed reads in conventional PCI mode.

PCI Interface Registers

PCI0 and PCI1 contain the same set of internal registers, but are located at different offsets.

A CPU access to the MV64460 PCIx Configuration register is performed via the PCIx Config-

uration Address and Data registers.

All PCI configuration registers are located at their standard offset in the configuration

header, as defined in the PCI specification, when accessed from their corresponding PCI

bus. For example, if a master on PCI1 performs a PCI configuration cycle on PCI’s Status and

Command register, the register is located at 0x004.

A host access from the PCI interface to this register allows the target PCI device to acknowl-

edge the interrupt by turning off the INTA* interrupt. Although the interrupts are active

low, the register values are active high. For example, a value of one in the INTA field indi-

cates that an interrupt is pending on INTA*. Also, writing a one to this location asserts the

INTA* interrupt.

The Katana

®

752i may generate interrupts to other PCI devices by accessing doorbell-type

interrupt-generating registers or address ranges within their PCI bridges. The board will

respond to interrupts caused by another PCI device when it accesses a programmable

range of local memory, as provided by the MV64460 memory controller. In addition, it may

Field: Value: Description:

Vendor ID 0x11AB Marvell

Device ID 0x6480 MV64460 System Controller

Subsystem Vendor ID 0x1223 Emerson Network Power

Subsystem Device ID 0x0048 Katana

®

752i