Processor: Processor Initialization

10006024-04 Katana

®

752i User’s Manual

4-7

PR0: PLL0 Range select bits.

PC1: PLL1 Configuration bits.

PRI: PLL1 Range bits.

Hardware Implementation Dependent 2 Register

Parity is implemented for the following arrays: I-Cache, I-Tag, D-Cache, D-Tag, and L2 Tag.

Status bits are set when a parity error is detected and cleared when the HID2 register is

written.

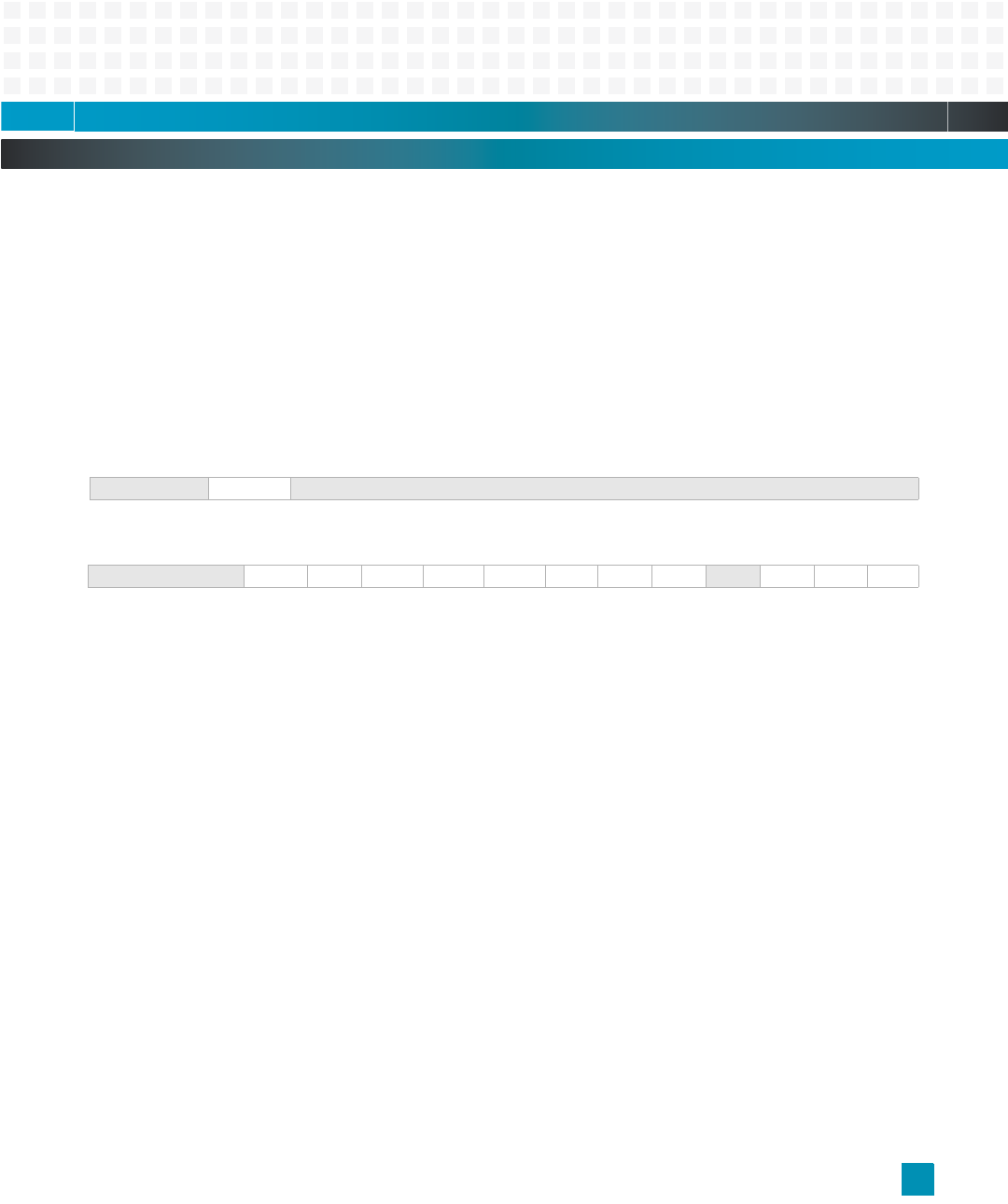

Register 4-3: 750GL Hardware Implementation Dependent, HID2

STMUMD: Disable store miss-under-miss processing.

FICBP: Force I-Cache bad parity.

FITBP: Force I-Tag bad parity.

FDCBP: Force D-Cache bad parity.

FDTBP: Force D-Tag bad parity.

FL2TBP: Force L2-Tag bad parity.

ICPS: L1 I-Cache/I-Tag Parity Error Status/Mask.

DCPS: L1 D-Cache/D-Tag Parity Error Status/Mask.

L2PS: L2 Tag Parity Error Status/Mask.

ICPE: L1 I-Cache/I-Tag Parity checking Enable.

DCPE: L1 D-Cache/D-Tag Parity checking Enable.

L2PE: L2 Tag Parity checking Enable.

0234 15

Reserved

STMUMD

Reserved

1

6

1

920 21 22 23 2425262728293031

Reserved FICBP

FITBP FDCBP FDTBP

FL2TBP

ICPS

DCPS

L2PS Res. ICPE

DCPE L2PE