Processor: JTAG/COP Headers

10006024-04 Katana

®

752i User’s Manual

4-13

JTAG/COP HEADERS

The 750GL CPU provides a dedicated user-accessible test access port (TAP) that is fully

compatible with the IEEE 1149.1 Standard Test Access Port and Boundary Scan Architec-

ture. The internal common-on-chip (COP) debug processor allows access to internal scan

chains for debugging purposes, and can also be used as a serial connection to the core for

emulator support.

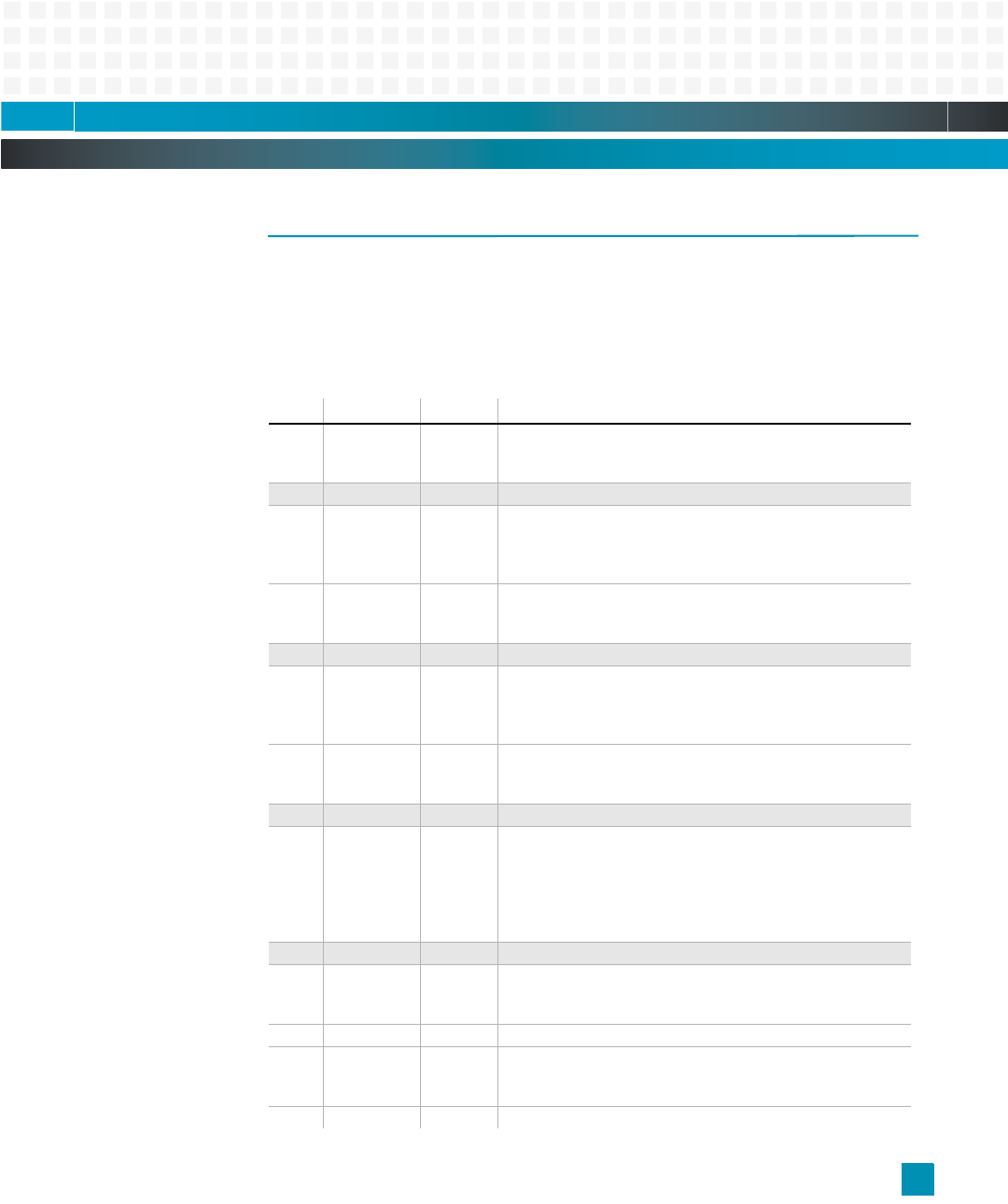

Table 4-6: 750GL JTAG/COP Interface Pin Assignments, (P3)

Pin: Signal: I/O: Description:

1 TDO Output The Test Data Out is a standard JTAG signal. This is the scan

path output, driven by the falling edge of the TCK signal and

sampled on the rising edge of TCK.

2 — — Not connected

3 TDI Input The Test Data In is a standard JTAG signal, and is the input

data for the scan path. TDI is driven by the JTAG controller on

the falling edge of TCK, and sampled on the rising edge of

TCK by the JTAG slave.

4 TRST* Input Test Reset is a standard JTAG signal. When this signal is active

(low), the JTAG logic is reset and inactive, allowing normal

operation of the 750GL.

5 — — Not connected

6 +3.3V Output This is the power supply for the 750GL which indicates to the

debug station the voltage at which the target processor is

powered. (For the

Katana

®

752i, this signal is tied to 2.5V

through a resettable PTC fuse.)

7 TCK Input The Test Clock is a standard JTAG signal, and is the clock for

the JTAG machine. JTAG signals are driven according to the

TCK falling edge and sampled over its rising edge.

8 — — Not connected

9 TMS Input The Test Mode Select is a standard JTAG signal. This signal,

along with TCK, controls the TAP controller state machine

allowing movement between its different states. When high,

it causes a change in the TAP controller state on the rising

edge of TMS. When low, the TAP controller state machine

remains in its current state.

10 — — Not connected

11 SRESET* Input The Soft Reset is required to enable the debug station to

either generate a Soft Reset sequence, or observe the 750GL

taking a Soft Reset sequence.

12 GND — Ground

13 HRESET* Input The Hard Reset is required to enable the debug station to

either generate a Hard Reset sequence, or observe the 750GL

taking a Hard Reset sequence.

14 Key — Pin 14 is not installed.