CTI 2572 Installation and Operation Guide

135

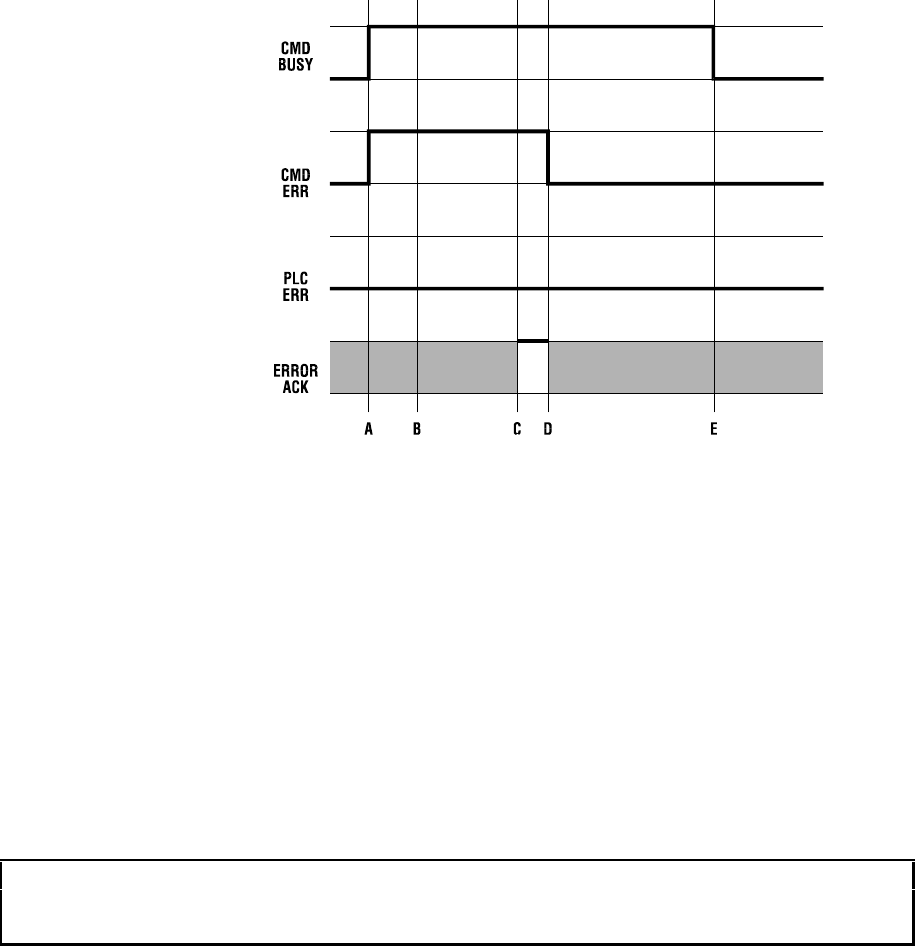

Command Error Timing

The module provides a mechanism for command execution communicating errors to the PLC. This

is accomplished via the CMD ERR bit and the ERROR WORD in the Command Block. The

following figure illustrates Command Error timing. Note that the shaded area indicates a "don’t care"

condition for the particular bit.

At time A, the module has

set CMD BUSY and is

attempting to retrieve the

command block and to

process the command.

Some time later, a

command processing error

occurs. The module writes

error information into the

error word of the

Command Block and

asserts CMD ERR at time

B. Processing of this

command is halted.

If the module cannot write

the error word to the

Command Block, it also

asserts the PLC ERR bit

(see the following section).

The error word is valid

only when CMD error is

asserted and PLC ERR is clear.

At the end of each PLC I/O scan, the module samples the state of ERROR ACK (Error

Acknowledge). As soon as the module detects that ERROR ACK is set (Time C), it will turn off

CMD ERR (and PLC ERR if on) at Time D and proceed with the error recovery.

After error recovery is competed, the module will clear CMD BUSY (Time E). This may or may not

be the in the same PLC I/O scan. CMD ERR will never be asserted unless CMD BUSY is asserted.

CMD ERR is always cleared prior to or at the same time as the release of the CMD BUSY signal

(Time D is always before or the same as time E).

NOTE:

The contents of the error word in the Command Block is valid only when CMD ERR is asserted and

PLC ERR is clear.

Since the ERROR ACK signal is sampled only when CMD ERR or PLC ERR is asserted, PLC logic

can leave the ERROR ACK bit on, if you wish to ignore all errors.

Figure 25. Command Error Timing