Intel® Server Board SE7520JR2 Functional Architecture

Revision 1.0

C78844-002

53

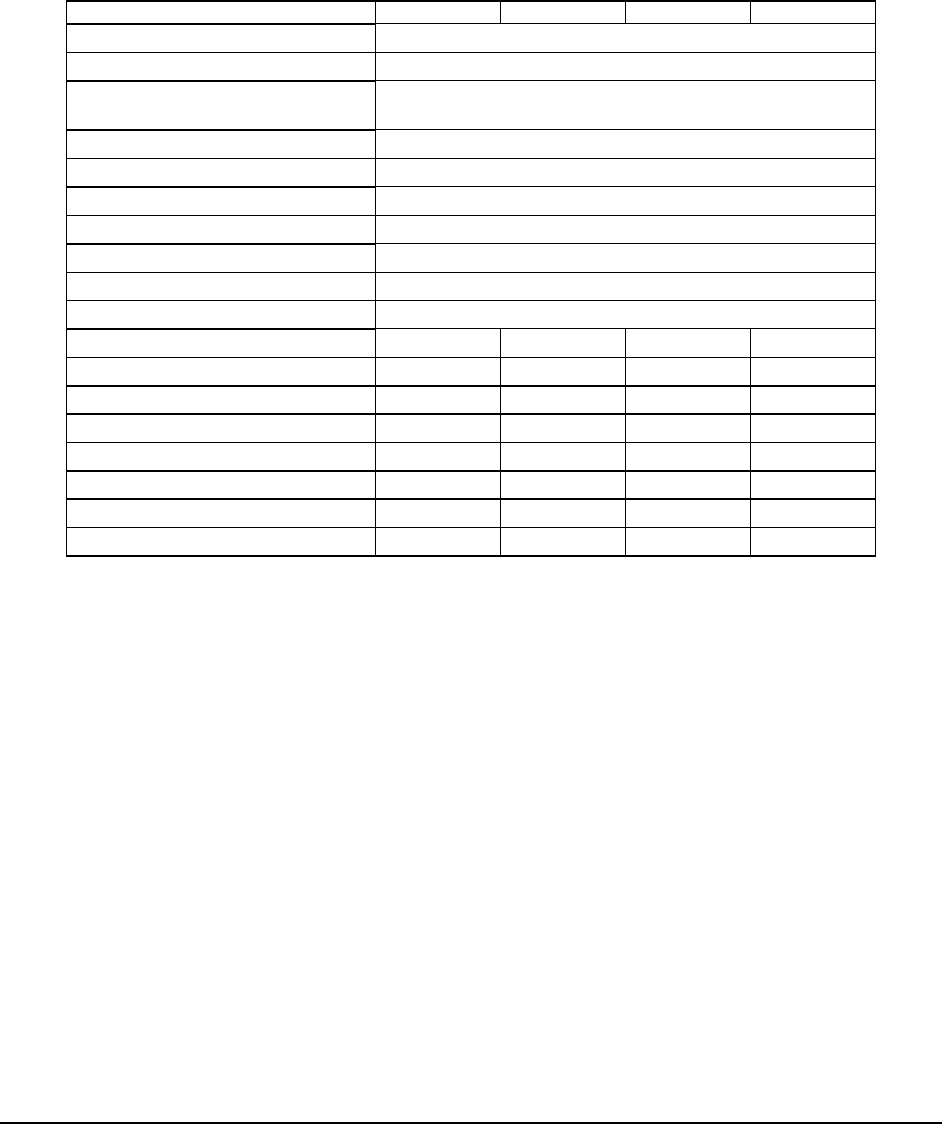

Both PCI and IRQ types of interrupts are handled by the ICH5-R. The ICH5-R translates these

to the APIC bus. The numbers in the table below indicate the ICH5-R PCI interrupt input pin to

which the associated device interrupt (INTA, INTB, INTC, INTD) is connected. The ICH5-R I/O

APIC exists on the I/O APIC bus with the processors.

Table 9: PCI Interrupt Routing/Sharing

Interrupt INT A INT B INT C INT D

Video ICH5R_PIRQB

IDE RAID ICH5R_PIRQC

NIC 10/100 (Not used on

SE7520JR2)

ICH5R_PIRQD

SIO ICH5R_SERIRQ

Legacy IDE ICH5R_PIRQ14

Legacy IDE ICH5R_PIRQ15

82546GB #1 P64A_IRQ6

82546GB #2 P64A_IRQ7

SCSI Controller #1 P64B_IRQ2

SCSI Controller #2 P64B_IRQ1

FL Riser TCK & TCO P64A_IRQ0 P64A_IRQ3 P64A_IRQ5 P64A_IRQ4

P64-A Slot 1 P64A_IRQ0 P64A_IRQ3 P64A_IRQ5 P64A_IRQ4

P64-A Slot 2 P64A_IRQ3 P64A_IRQ5 P64A_IRQ4 P64A_IRQ0

P64-A Slot 3 P64A_IRQ5 P64A_IRQ4 P64A_IRQ2 P64A_IRQ1

LP Riser P64B_IRQ4 P64B_IRQ3 P64B_IRQ2 P64B_IRQ1

P64-B Slot 1 P64B_IRQ4 P64B_IRQ3 P64B_IRQ2 P64B_IRQ1

P64-B Slot 2 P64B_IRQ3 P64B_IRQ2 P64B_IRQ1 P64B_IRQ4

P64-B Slot 3 P64B_IRQ2 P64B_IRQ1 P64B_IRQ4 P64B_IRQ3

3.4.3.2 APIC Interrupt Routing

For APIC mode, the Server Board SE7520JR2 interrupt architecture incorporates three Intel I/O

APIC devices to manage and broadcast interrupts to local APICs in each processor. The Intel

I/O APICs monitor each interrupt on each PCI device including PCI slots in addition to the ISA

compatibility interrupts IRQ(0-15). When an interrupt occurs, a message corresponding to the

interrupt is sent across a three-wire serial interface to the local APICs. The APIC bus minimizes

interrupt latency time for compatibility interrupt sources. The I/O APICs can also supply greater

than 16 interrupt levels to the processor(s). This APIC bus consists of an APIC clock and two

bidirectional data lines.