Functional Architecture Intel® Server Board SE7520JR2

Revision 1.0

C78844-002

70

3.5 Configuration and Initialization

This section describes the initial programming environment including address maps for memory

and I/O, techniques and considerations for programming ASIC registers, and hardware options

configuration.

3.5.1 Memory Space

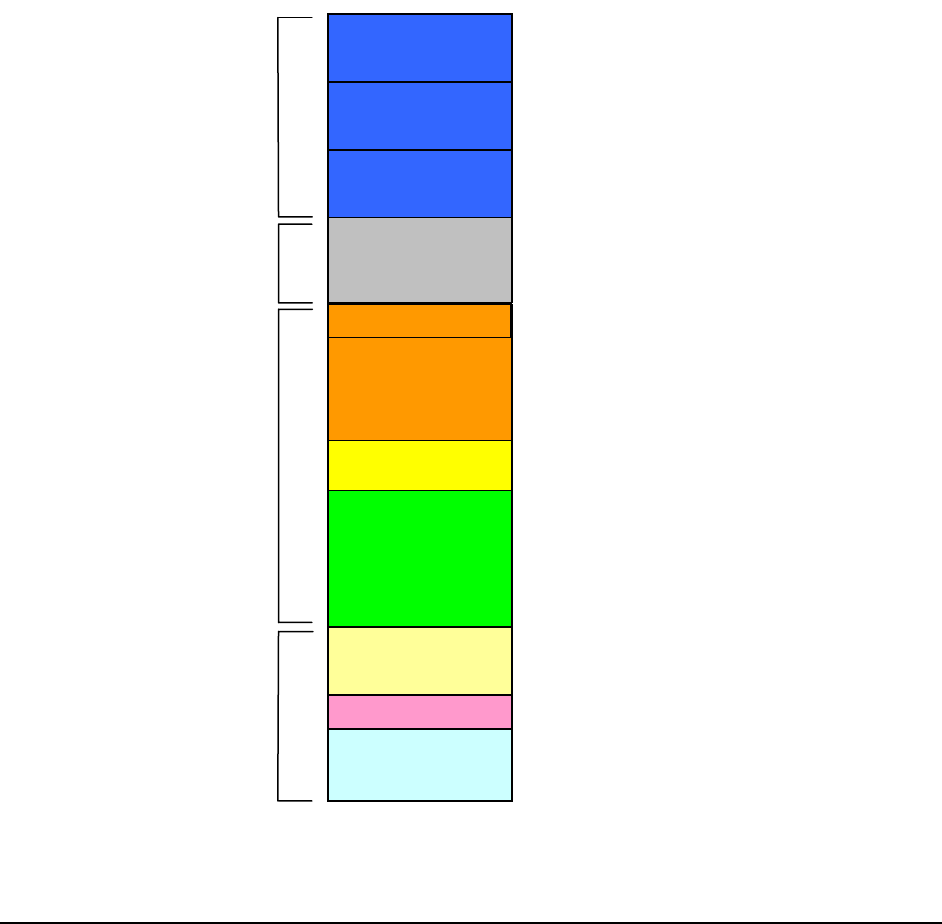

At the highest level, the Intel Xeon processor address space is divided into four regions, as

shown in the following figure. Each region contains the sub-regions that are described in

following sections. Attributes can be independently assigned to regions and sub-regions using

registers. The Intel E7520 chipset supports 64GB of host-addressable memory space and

64KB+3 of host-addressable I/O space. The Server Board SE7520JR2 supports only the main

memory up to 24GB for DDR-266 or up to 16GB for DDR333/DDR2-400.

Figure 14. Intel

®

Xeon™ Processor Memory Address Space

4GB

Optional ISA Hole

Top of Low Memory (TOLM)

16MB

15MB

1MB

640KB

512KB

0

A

dditional Main

Memory Address

Ran

g

e

Main Memory

A

ddress Range

DOS Legacy

A

ddress Range

Lo PCI Memory

Space Range

TSEG SMRAM Space

64GB

Hi PCI Memory

A

ddress Range

Upper Memory

Ranges