94 Rabbit 3000 Microprocessor

The code to do this may also hit the watchdog with a 0.25-second period to speed up the

reset. Such watchdog code must be written so that it is highly unlikely that a crash will

incorporate the code and continue to hit the watchdog in an endless loop. The following

suggestions will help.

1. Place a jump to self before the entry point of the watchdog hitting routines. This pre-

vents entry other than by a direct call or jump to the routine.

2. Before calling the routine, set a data byte to a special value and then check it in the rou-

tine to make sure the call came from the right caller. If not, go into an endless loop with

interrupts disabled.

3. Maintain data corruption flags and/or checksums. If these go wrong, go into an endless

loop with interrupts off.

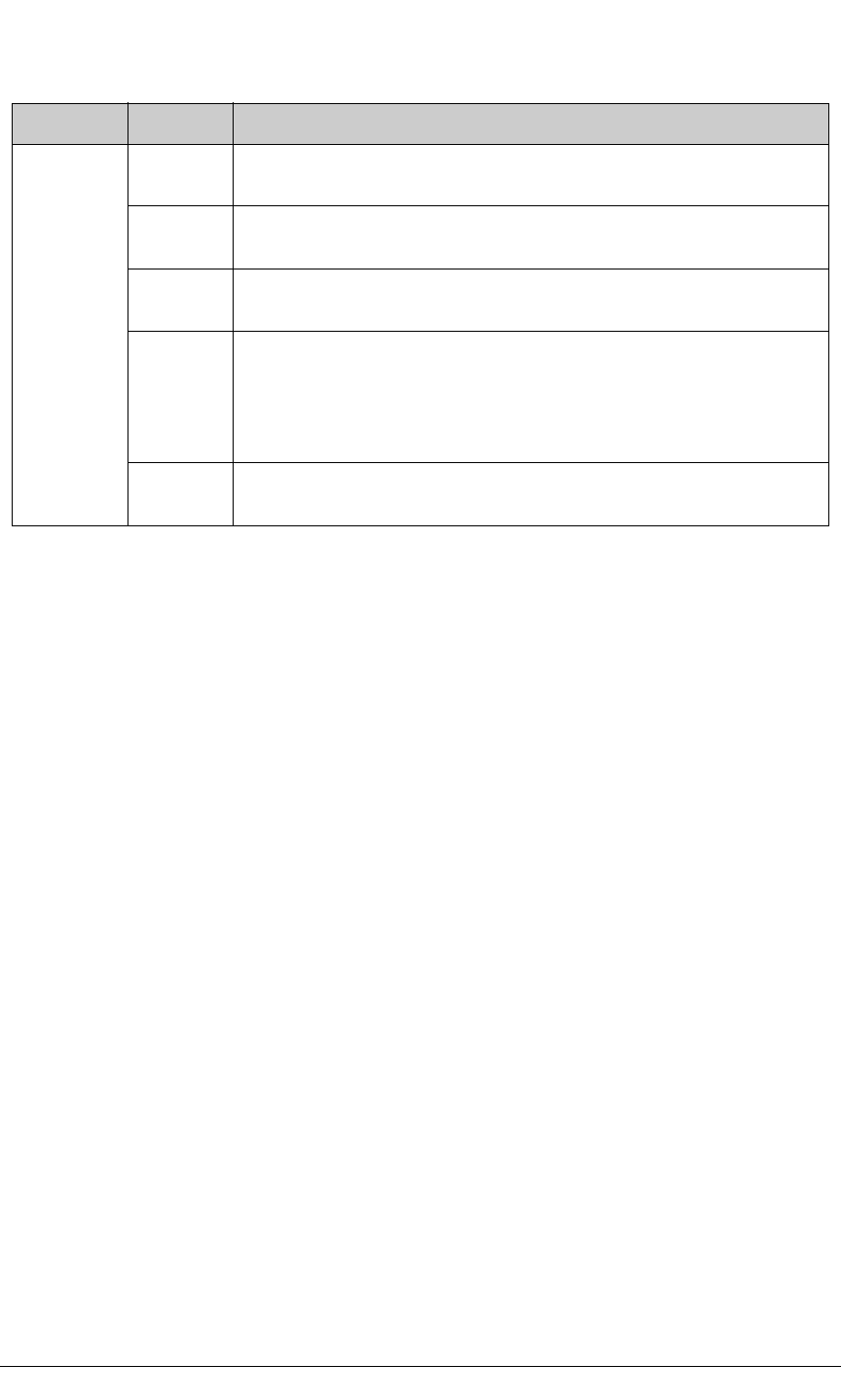

Table 7-13. Watchdog Timer Test Register (WDTTR adr = 0x09)

Bit(s) Value Description

7:0

0x51

Clock the least significant byte of the watchdog timer from the peripheral

clock. (Intended for chip test and code 0x54 below only.)

0x52

Clock the most significant byte of the watchdog timer from the peripheral

clock. (Intended for chip test and code 0x54 below only.)

0x53

Clock both bytes of the watchdog timer, in parallel, from the peripheral

clock. (Intended for chip test and code 0x54 below only.)

0x54

Disable the watchdog timer. This value, by itself, does not disable the

watchdog timer. Only a sequence of two writes, where the first write is

0x51, 0x52, or 0x53, followed by a write of 0x54, actually disables the

watchdog timer. The watchdog timer will be re-enabled by any other write

to this register.

other

Normal clocking (32 kHz oscillator) for the watchdog timer. This is the

condition after reset.