224 Rabbit 3000 Microprocessor

The following I/O read time delays were measured.

The measurements were taken at the 50% points under the following conditions.

• T = -40°C to 85°C, V = 3.3 V

• Internal clock to nonloaded CLK pin delay ≤ 1 ns @ 85°C/3.0 V

The following I/O write time delays were measured.

The measurements were taken at the 50% points under the same conditions that the I/O

read delays were measured.

I/O bus cycles have an automatic wait state and thus require 3 clocks plus any extra wait

states specified.

See Table 16-2 for delays at other voltages.

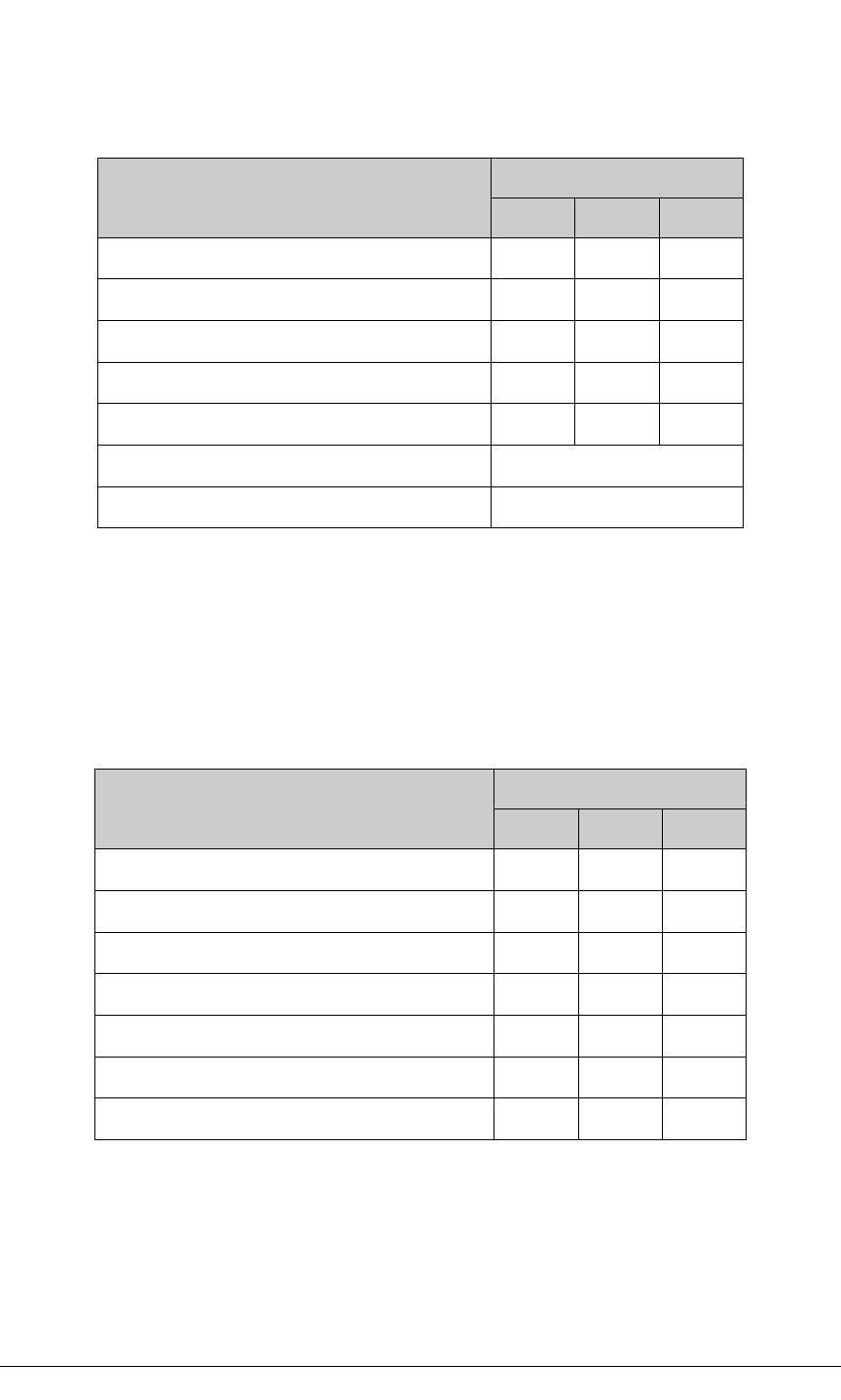

Table 16-5. I/O Read Time Delays

Time Delay

Output Capacitance

30 pF 60 pF 90 pF

Max. clock to address delay (T

adr

)

6 ns 8 ns 11 ns

Max. clock to memory chip select delay (T

CSx

)

6 ns 8 ns 11 ns

Max. clock to I/O chip select delay (T

IOCSx

)

6 ns 8 ns 11 ns

Max. clock to I/O read strobe delay (T

IORD

)

6 ns 8 ns 11 ns

Max. clock to I/O buffer enable delay (T

BUFEN

)

6 ns 8 ns 11 ns

Min. data setup time (T

setup

)

1 ns

Min. data hold time (T

hold

)

0 ns

Table 16-6. I/O Write Time Delays

Time Delay

Output Capacitance

30 pF 60 pF 90 pF

Max. clock to address delay (T

adr

)

6 ns 8 ns 11 ns

Max. clock to memory chip select delay (T

CSx

)

6 ns 8 ns 11 ns

Max. clock to I/O chip select delay (T

IOCSx

)

6 ns 8 ns 11 ns

Max. clock to I/O write strobe delay (T

IOWR

)

6 ns 8 ns 11 ns

Max. clock to I/O buffer enable delay (T

BUFEN

)

6 ns 8 ns 11 ns

Max. high Z to data valid rel. to clock (T

DHZV

)

10 ns 12 ns 15 ns

Max. data valid to high Z rel. to clock (T

DVHZ

)

10 ns 12 ns 15 ns