320 Rabbit 3000 Microprocessor

The I/O banks on Port E (enabled for the User mode by IBUER) have a slightly different

operation in the User mode. Disabling user access to a given I/O bank not only causes

writes to the corresponding IBxCR register to be ignored in the User mode, but also inhib-

its the strobe associated with that I/O bank.

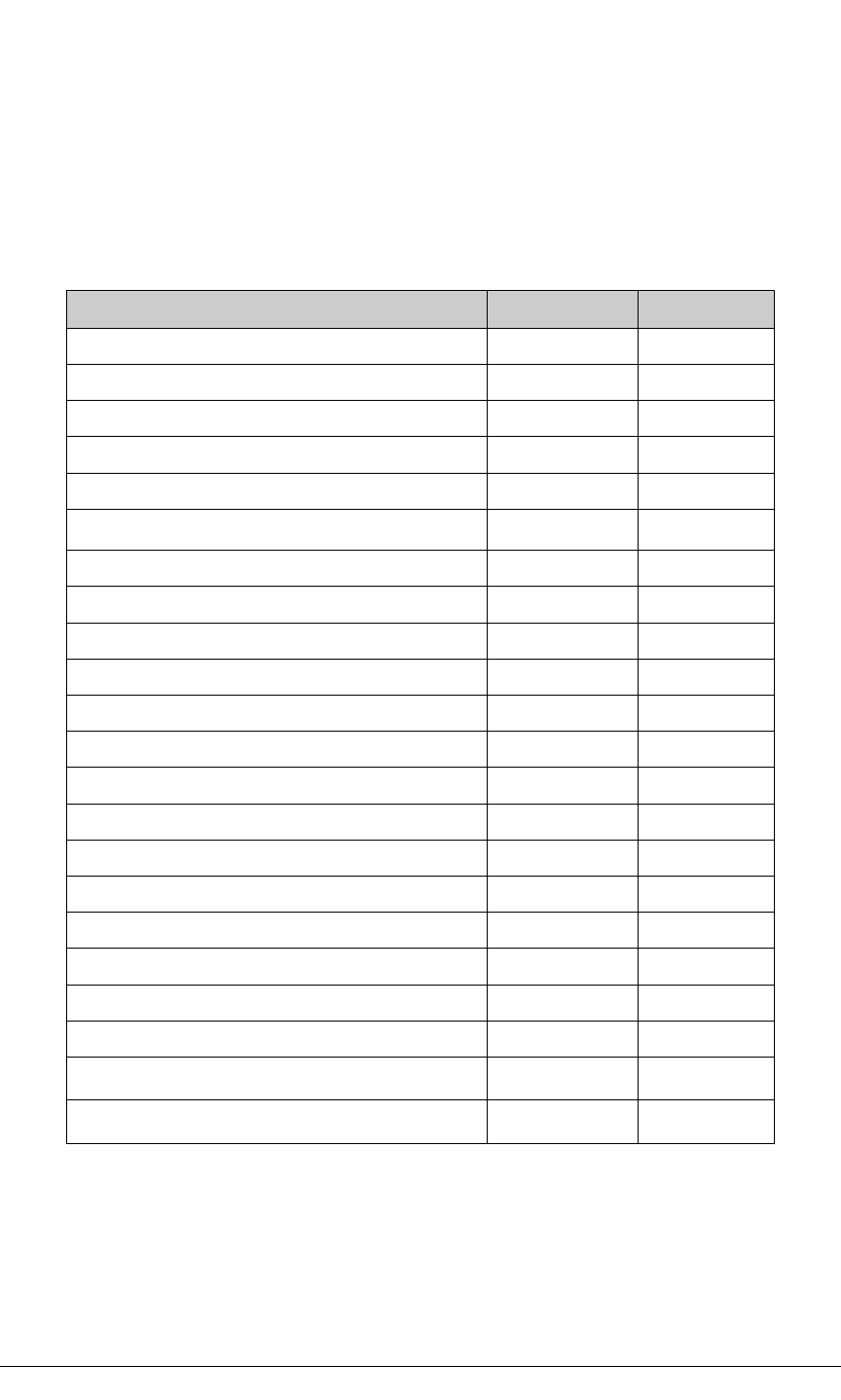

Access to the internal I/O registers listed in Table C-4 is always denied in the User mode.

Table C-4. I/O Addresses Inaccessible in User Mode

Register Name Mnemonic I/O Address

Global Control/Status Register GCSR 0x0000

Watchdog Timer Control Register WDTCR 0x0008

Watchdog Timer Test Register WDTTR 0x0009

Global Clock Modulator 0 Register GCM0R 0x000A

Global Clock Modulator 1 Register GCM1R 0x000B

Secondary Watchdog Timer Register

*

* These registers are only available on the Rabbit 3000A.

SWDTR 0x000C

Global Power Save Control Register GPSCR 0x000D

Global Output Control Register GOCR 0x000E

Global Clock Double Register GCDR 0x000F

MMU Instruction/Data Register MMIDR 0x0010

Stack Segment Register STACKSEG 0x0011

Data Segment Register DATASEG 0x0012

Segment Size Register SEGSIZE 0x0013

Memory Bank 0 Control Register MB0CR 0x0014

Memory Bank 1 Control Register MB1CR 0x0015

Memory Bank 2 Control Register MB2CR 0x0016

Memory Bank 3 Control Register MB3CR 0x0017

MMU Expanded Code Register MECR 0x0018

Memory Timing Control Register MTCR 0x0019

Breakpoint/Debug Control Register BDCR 0x001C

User Enable registers

*

0x03xx

Memory Protection registers

*

0x04xx