User’s Manual 151

For seven of the counters (A1–A7), the terminal count condition is reported in a status regis-

ter and can be programmed to generate an interrupt. There is one interrupt vector for Timer

A and a common interrupt priority. A common status register (TACSR) has a bit for each

timer that indicates if the output pulse for that timer has taken place since the last read of the

status register. When the status register is read, these bits are cleared. No bit will be lost.

Either it will be read by the status register read or it will be set after the status register read is

complete. If a bit is on and the corresponding interrupt is enabled, an interrupt will occur

when priorities allow. However, a separate interrupt is not guaranteed for each bit with an

enabled interrupt. If the bit is read in the status register, it is cleared and no further interrupt

corresponding to that bit will be requested. It is possible that one bit will cause an interrupt,

and then one or more additional bits will be set before the status register is read. After these

bits are cleared, they cannot cause an interrupt. If any bits are on, and the corresponding

interrupt is enabled, then the interrupt will take place as soon as priorities allow. However, if

the bit is cleared before the interrupt is latched, the bit will not cause an interrupt. The proper

rule to follow is for the interrupt routine to handle all bits that it sees set.

Although timers A8–A10 are part of Timer A, they are dedicated to the input pulse cap-

ture, PWM, and quadrature decoder peripherals respectively. The peripherals clocked by

these timers can generate interrupts but the timers themselves cannot. Furthermore, these

timers cannot be cascaded with Timer A1.

11.1.1 Timer A I/O Registers

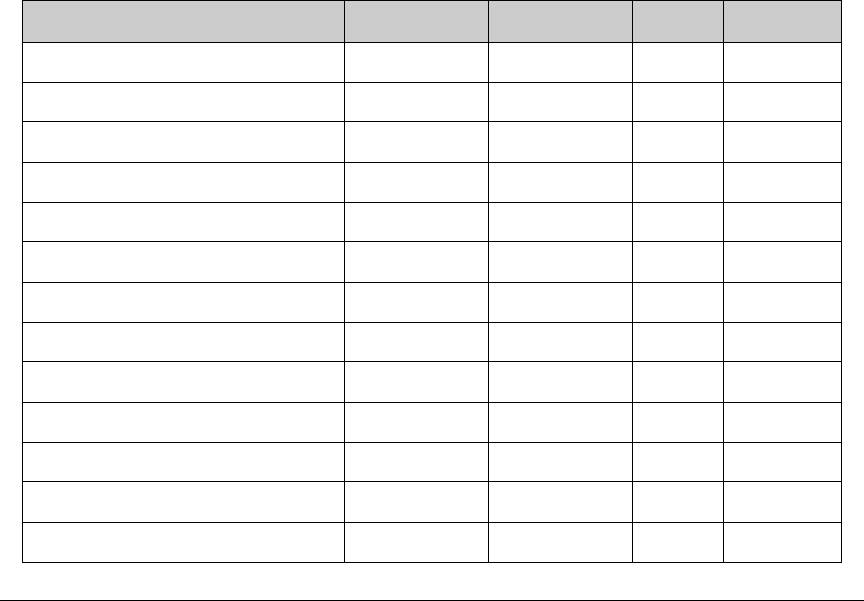

The I/O registers for Timer A are listed in Table 11-1.

Table 11-1. Timer A I/O Registers

Register Name Mnemonic I/O address R/W Reset

Timer A Control/Status Register TACSR 0xA0 R/W 00000000

Timer A Prescale Register TAPR 0xA1 W xxxxxxx1

Timer A Time Constant 1 Register TAT1R 0xA3 W xxxxxxxx

Timer A Control Register TACR 0xA4 W 00000000

Timer A Time Constant 2 Register TAT2R 0xA5 W xxxxxxxx

Timer A Time Constant 8 Register TAT8R 0xA6 W xxxxxxxx

Timer A Time Constant 3 Register TAT3R 0xA7 W xxxxxxxx

Timer A Time Constant 9 Register TAT9R 0xA8 W xxxxxxxx

Timer A Time Constant 4 Register TAT4R 0xA9 W xxxxxxxx

Timer A Time Constant 10 Register TAT10R 0xAA W xxxxxxxx

Timer A Time Constant 5 Register TAT5R 0xAB W xxxxxxxx

Timer A Time Constant 6 Register TAT6R 0xAD W xxxxxxxx

Timer A Time Constant 7 Register TAT7R 0xAF W xxxxxxxx