190 Rabbit 3000 Microprocessor

clock rate must be very small, and depends on the longest possible run of zeros in the

received frame. NRZI encoding guarantees at least one transition every six bits (with the

inserted zeros). Since the DPLL can adjust by two counts every bit cell, the maximum dif-

ference between the sending data rate and the DPLL output clock rate is 1/48 (~2%).

With Biphase data encoding (either -Level, -Mark or -Space), the DPLL runs only as long

as transitions are present in the receive data stream. Two consecutive missed transitions

causes the DPLL to halt operation and wait for the next available transition. This mode of

operation is necessary because it is possible for the DPLL to lock onto the optional transi-

tions in the receive data stream. Since they are optional, they will eventually not be

present and the DPLL can attempt to lock onto the required transitions. Since the DPLL

can adjust by one count every bit cell, the maximum difference between the sending data

rate and the DPLL output clock rate is 1/16 (~6%).

With Biphase data encoding the DPLL is designed to work in multiple-access conditions

where there may not be Flags on an idle line. The DPLL will properly generate an output

clock based on the first transition in the leading zero of an opening Flag. Similarly, only the

completion of the closing Flag is necessary for the DPLL to provide the extra two clocks to

the receiver to properly assemble the data. In Biphase-Level mode, this means the transi-

tion that defines the last zero of the closing Flag. In Biphase-Mark and Biphase-Space

modes this means the transition that defines the end of the last zero of the closing Flag.

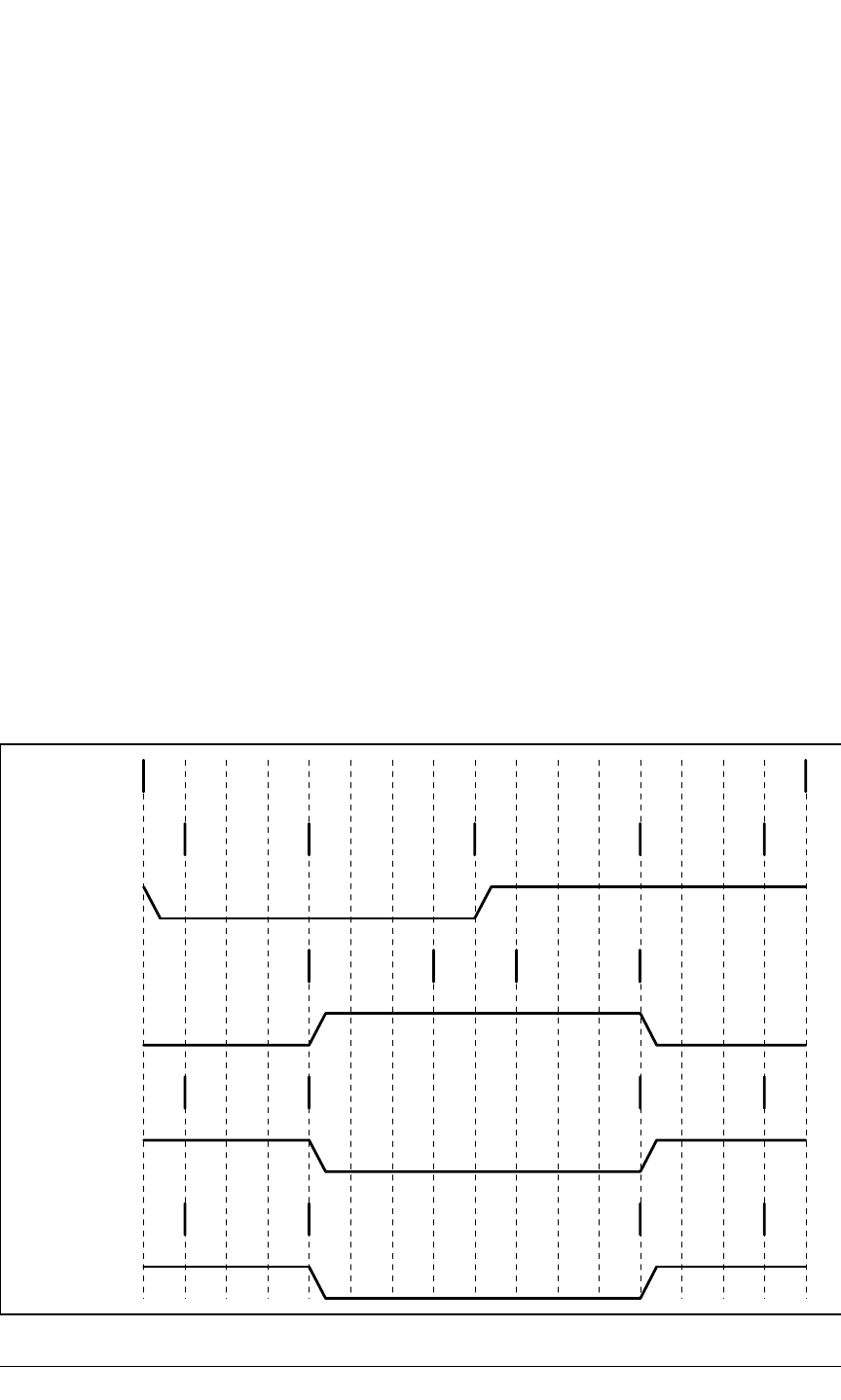

The figure below shows the adjustment ranges and output clock for the different modes of

operation of the DPLL. Each mode of operation will be described in turn.

Bit cell

Bi-S adj

Bi-M adj

NRZI adj

NRZI Clock

Bi-L Clock

Bi-L adj

Bi-S Clock

Bi-M Clock

nonenone add one add two subtract two subtract one

none add oneignore transitions subtract one

nonenone add one ignore transitions subtract one

nonenone add one ignore transitions subtract one

ignore transitions