82 Rabbit 3000 Microprocessor

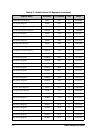

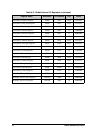

Table 7-5. Global Control/Status Register

Global Control/Status Register (GCSR) (Address = 0x00)

Bit(s) Value Description

7:6

(rd-only)

00 No Reset or Watchdog Timer time-out since the last read.

01

The Watchdog Timer timed out. These bits are cleared by a read of this

register.

10 This bit combination is not possible.

11 Reset occurred. These bits are cleared by a read of this register.

5

0 No effect on the Periodic interrupt. This bit will always be read as zero.

1 Force a Periodic interrupt to be pending.

4:2 xxx See table below for decode of this field.

1:0

00 Periodic interrupts are disabled.

01 Periodic interrupts use Interrupt Priority 1.

10 Periodic interrupts use Interrupt Priority 2.

11 Periodic interrupts use Interrupt Priority 3.

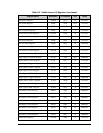

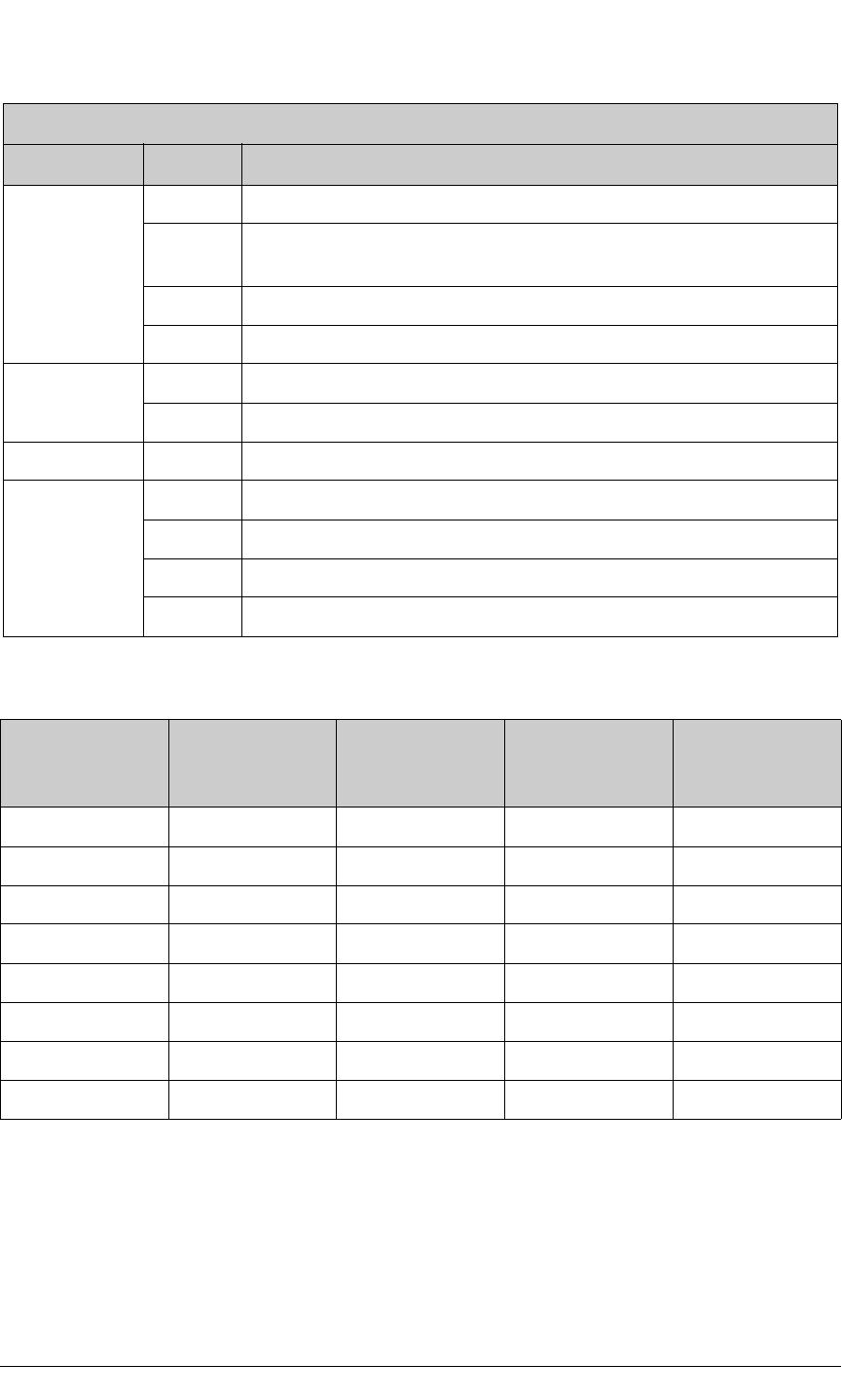

Table 7-6. Clock Select Field of GCSR

Clock Select

Bits 4:2 GCSR

CPU Clock

Peripheral

Clock

Main

Oscillator

Power-Save CS

if Enabled by

GPSCR

000 osc/8 osc/8 on short CS option

001 osc/8 osc on short CS option

010 osc osc on none

011 osc/2 osc/2 on none

100 32 kHz or fraction 32 kHz or fraction on self-timed option

101 32 kHz or fraction 32 kHz or fraction off self-timed option

110 osc/4 osc/4 on short CS option

111 osc/6 osc/6 on short CS option