88 Rabbit 3000 Microprocessor

When operating in the 32 kHz mode, it is also possible to further divide the clock to a fre-

quency as low as 2 kHz, further reducing execution speed and current consumption.

It is anticipated that these measures would reduce operating current consumption to as low as

20 µA plus some additional leakage that would be significant at high operating temperatures.

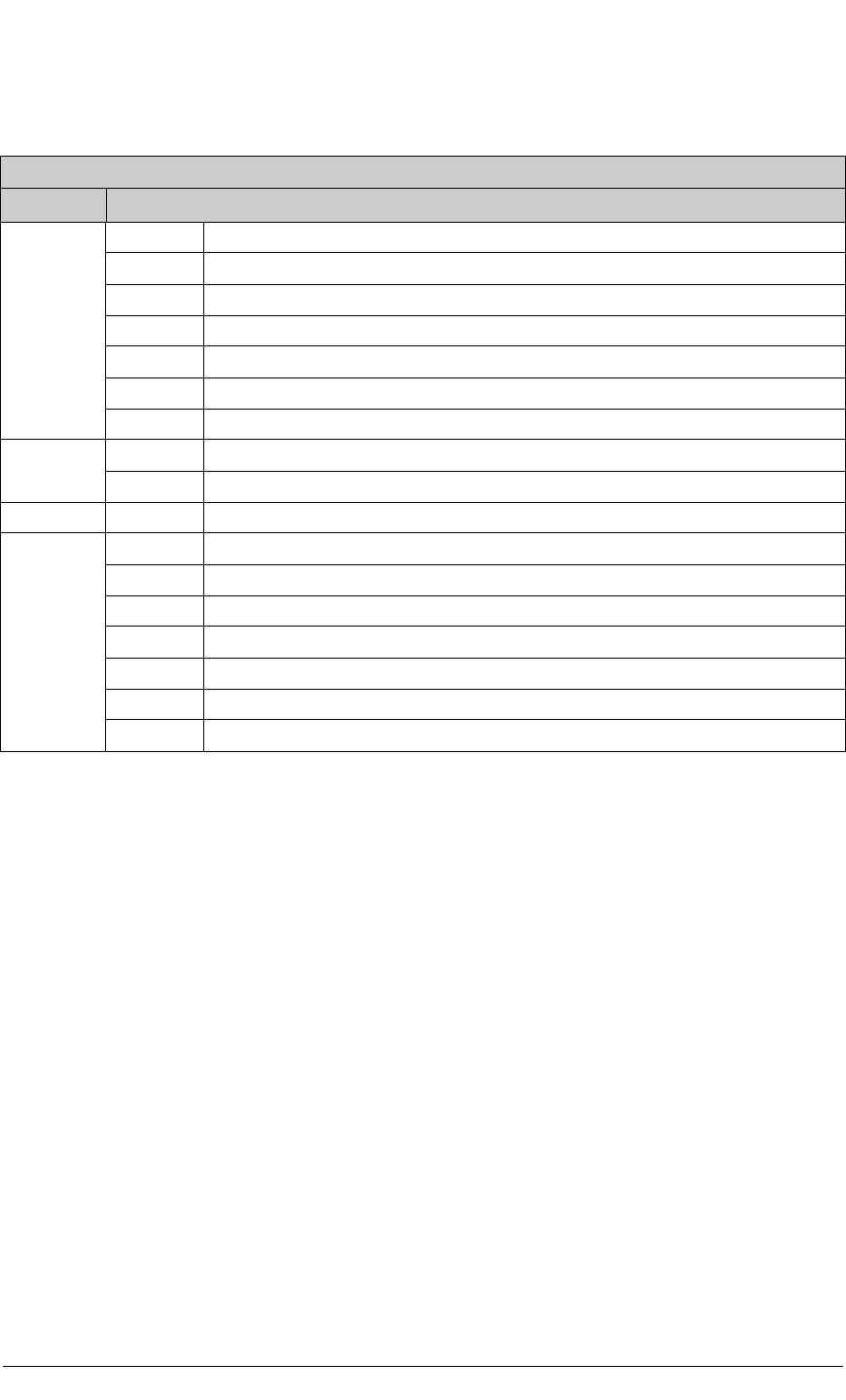

Global Power Save Control Register (GPSCR) (Address = 0x0D)

Bit(s) Value Description

7:5

000 Self-timed chip selects are disabled.

001 This bit combination is reserved and should not be used.

01x This bit combination is reserved and should not be used.

100 296 ns self-timed chip selects (192 ns best case, 457 ns worst case).

101 234 ns self-timed chip selects (151 ns best case, 360 ns worst case).

110 171 ns self-timed chip selects (111 ns best case, 264 ns worst case).

111 109 ns self-timed chip selects (71 ns best case, 168 ns worst case).

4

0 Normal Chip Select operation.

1 Short Chip Select timing when dividing main oscillator by 4, 6, or 8.

3 x This bit is reserved and should not be used.

2:0

000 The 32 kHz clock divider is disabled.

001 This bit combination is reserved and should not be used.

01x This bit combination is reserved and should not be used.

100 32 kHz oscillator divided by two (16.384 kHz).

101 32 kHz oscillator divided by four (8.192 kHz).

110 32 kHz oscillator divided by eight (4.096 kHz).

111 32 kHz oscillator divided by sixteen (2.048 kHz).