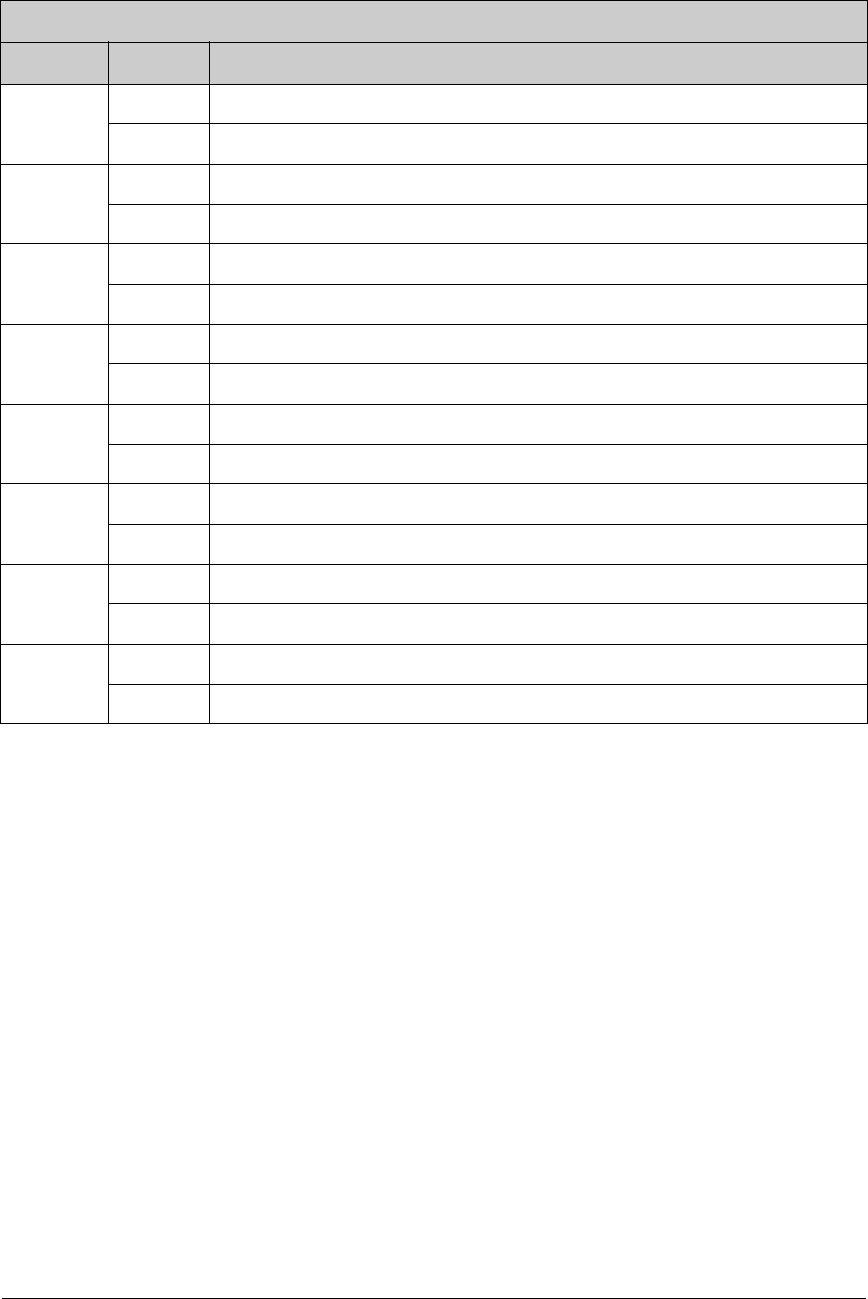

User’s Manual 153

4

(write)

0 A4 interrupt disabled.

1 A4 interrupt enabled.

3

(read)

0 A3 counter has not reached its terminal count.

1 A3 count done. This status bit is cleared by a read of this register.

3

(write)

0 A3 interrupt disabled.

1 A3 interrupt enabled.

2

(read)

0 A2 counter has not reached its terminal count.

1 A2 count done. This status bit is cleared by a read of this register.

2

(write)

0 A2 interrupt disabled.

1 A2 interrupt enabled.

1

(read)

0 A1 counter has not reached its terminal count.

1 A1 count done. This status bit is cleared by a read of this register.

1

(write)

0 A1 interrupt disabled.

1 A1 interrupt enabled.

0

(write-only)

0 Disable Timer A main clock (perclk/2).

1 Enable Timer A main clock (perclk/2).

Table 11-3. Timer A Control and Status Register (continued)

Timer A Control and Status Register (TACSR) (Address = 0x00A0)

Bit(s) Value Description