Instruction Classification

4-28

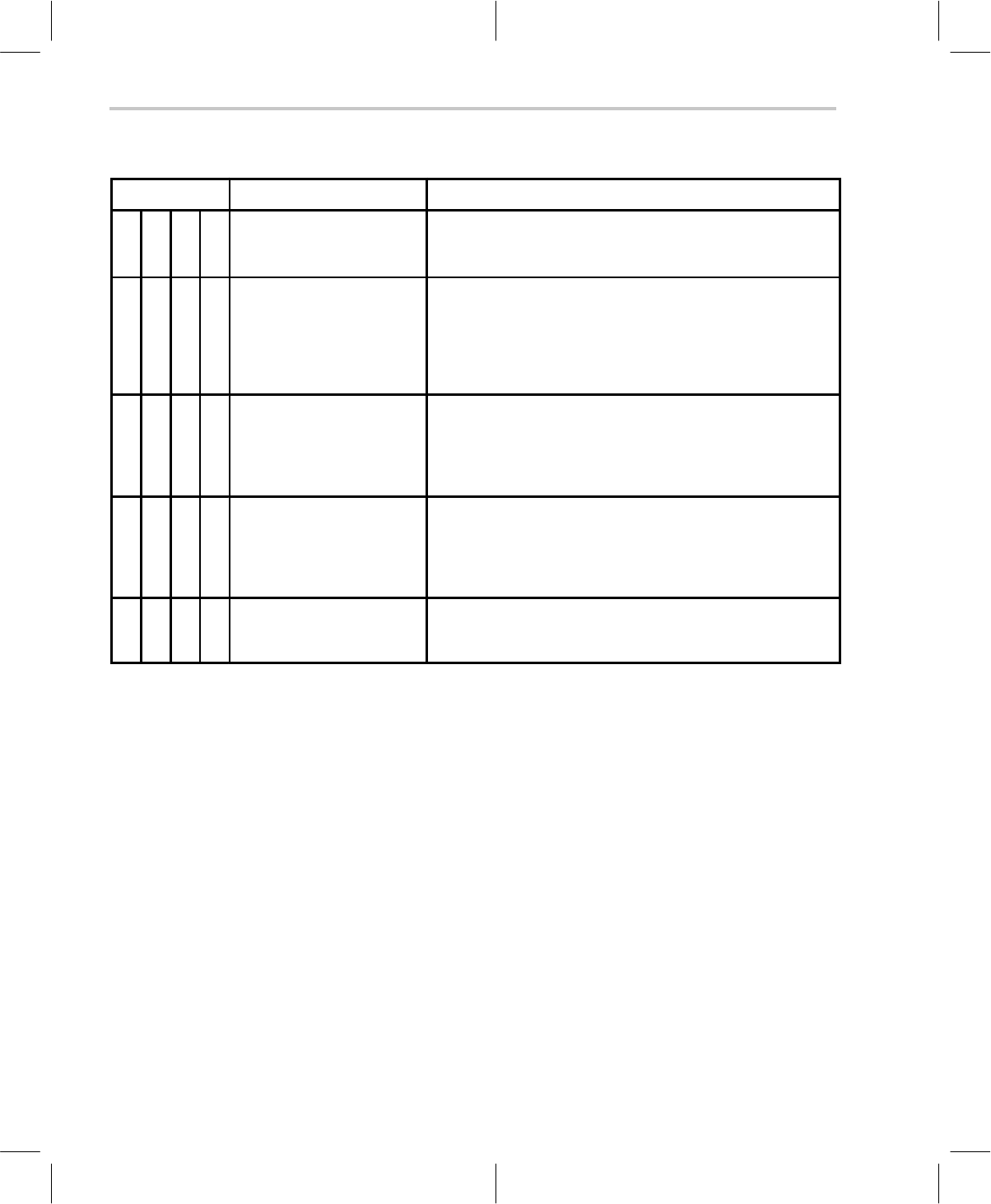

Table 4–15. Class 1b Instruction Description (Continued)

C1b Mnemonic Description

1 0 1 1 MULAPL An, {adrs}

MULAPLS An, {adrs}

Multiply the MR register by the addressing mode {adrs} and add

the lower 16 bits of the product to the accumulator. Latch the

upper 16 bits into the PH register. ALU status is modified.

1 1 0 0 SHLTPL An, {adrs}

SHLTPLS An, {adrs}

Shift left n bits (SV reg). The 16-bit contents of the data memory

location in {adrs} are shifted and placed in accumulator (string)

An. Zeros fill from the right and either zeros or ones fill the left

depending on the sign (assuming XSGM mode is set). Transfer

the lower 16 bits to the accumulator and latch the upper 16 bits

in PH. ALU status is modified.

1 1 0 1 SHLSPL An, {adrs}

SHLSPLS An, {adrs}

Shift left n bits (SV reg ). The contents of the data memory

location in {adrs} are placed in a 32-bit result. Zeros fill from the

right and either zeros or sign extended ones fill the left (if XSGM

mode is set). Subtract the lower 16 bits from the accumulator

and latch the upper 16 bits in PH. ALU status is modified.

1 1 1 0 SHLAPL An, {adrs}

SHLAPLS An, {adrs}

Shift left n bits (SV reg). The contents of the data memory loca-

tion in {adrs} are placed into a 32-bit result. Zeros fill the right

and either zeros or sign extended ones fill the left (in XSGM

mode). Add the lower 16 bits to the accumulator and latch the

upper 16 bits in PH. ALU status is modified.

1 1 1 1 MULSPL An, {adrs}

MULSPLS An, {adrs}

Multiply the MR register by the contents of {adrs} and subtract

the lower 16 bits of the product from the accumulator. Latch the

upper 16 bits into the PH register. ALU status is modified.

4.4.2 Class 2 Instructions: Accumulator and Constant Reference

These instructions provide the capability to reference short (8 bits) or long (16

bits or (n

S

+2) * 16-bit string) constants stored in program memory and to

execute arithmetic and logical operations between accumulator contents and

these constants. Since the MSP50P614/MSP50C614 is a Harvard type

processor, these instructions are necessary and distinct from the general class

of memory reference instructions. Subclass 2a, listed belows include

references between accumulator and short 8-bit constants. This class has the

advantage of requiring only 1 instruction word to code and 1 instruction cycle

to execute Thus is particularly useful for control variables such as loop counts,

indexes, etc. The short constants also provide full capability for byte

operations in a single instruction word.

Subclass 2b references accumulator and long constants from program

memory (16 bits for non string constants and (n

S

+2) * 16 bits for string

constants). Class 2b instructions take 2 instruction words to code. The execu-

tion of these instructions is 2 instruction cycles when the long constant is a

single word. The execution is n

S

+2 execution cycles for n

S

word string