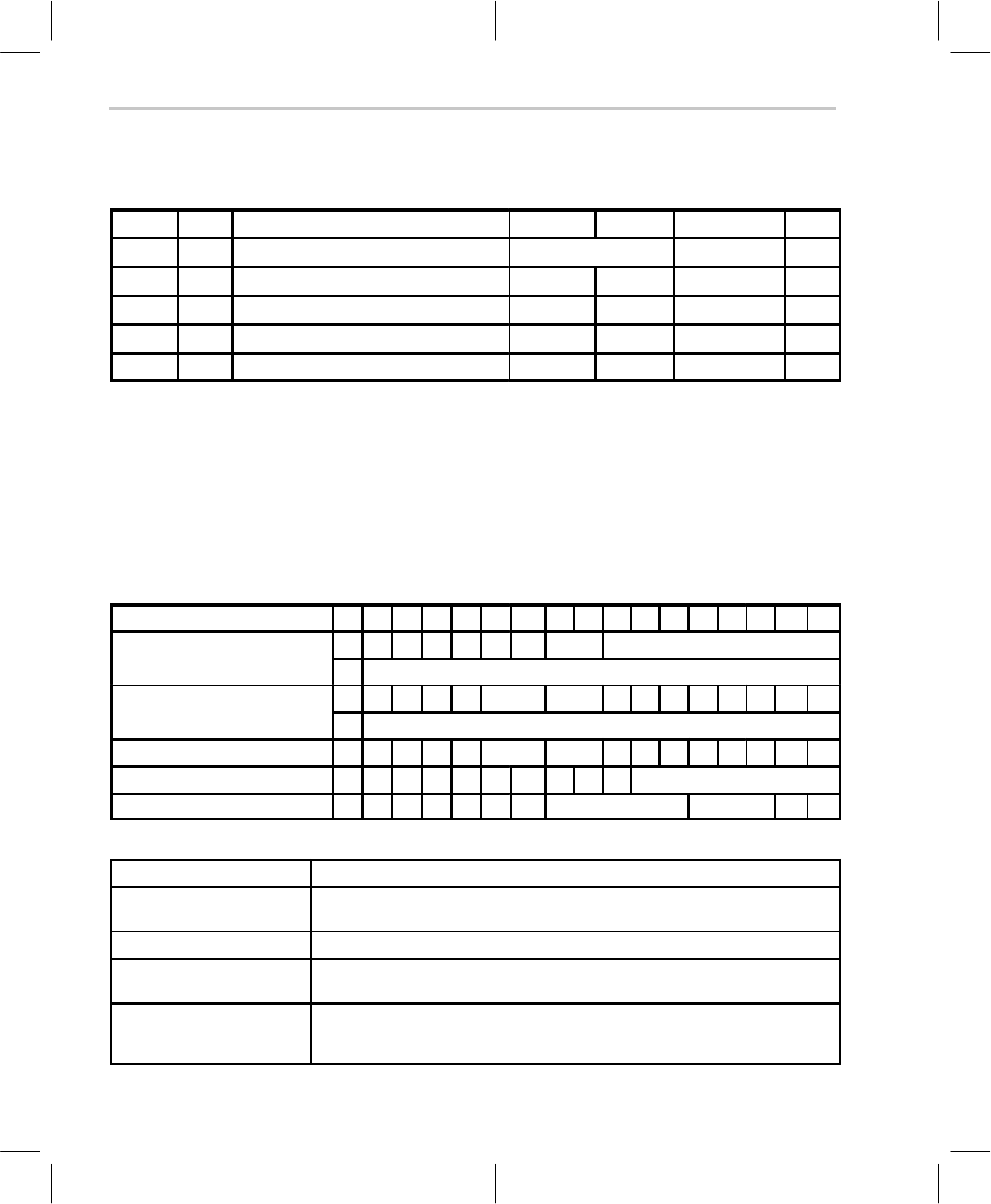

Individual Instruction Descriptions

4-80

4.14.4 AND Bitwise AND

Syntax

[label] name dest, src [, src1] [, mod] Clock, clk Word, w With RPT, clk Class

AND An, {adrs} Table 4–46 Table 4–46 1b

AND An[~], An[~], imm16 [, next A] 2 2 N/R 2b

AND An[~], An~, An [, next A] 1 1 n

R

+3 3

AND TFn, [!]{flagadrs} 1 1 N/R 8a

AND TFn, {cc} [, Rx] 1 1 n

R

+3 8b

Execution [premodify AP if mod specified]

dest ⇐ dest AND src (for two operands)

dest ⇐ src AND src1 (for three operands)

PC ⇐ PC + w

Flags Affected dest is An:OF, SF, ZF, CF are set accordingly

dest is TFn:TFn bits in STAT register are set accordingly

src is {adrs}: TAG bit is set accordingly

src is {flagadrs}: TAG bit is set accordingly

Opcode

Instructions 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AND An, {adrs}

0 1 0 0 0 1 0 An adrs

x dma16 (for direct) or offset16 (long relative) [see section 4.13]

AND An[~], An[~], imm16 [, next A]

1 1 1 0 0 next A An 1 0 1 0 0 1 A~ ~A

x imm16

AND An[~], An~, An [, next A] 1 1 1 0 0 next A An 0 1 0 1 0 0 A~ ~A

AND TFn, {flagadrs} 1 0 0 1 1 flg Not 1 0 0 flagadrs

AND TFn, {cc} [, Rx] 1 0 0 1 0 flg Not cc Rx 1 0

Description

Syntax Description

AND dest, src, src1 [, mod] Bitwise AND src1 and src and store result in dest. Premodification of accumulator

pointers are allowed with some operand types.

AND dest, src Bitwise AND dest and src and store result in dest.

AND TFn, {flagadrs} AND TFn bit with 17

th

bit of data memory address referred by addressing mode

{flagadrs}, store result in TFn bit in STAT register. n is either 1 or 2.

AND TFn, {cc} [, Rx] AND test condition {cc} with TFn bit in STAT register. Rx must be provided if cc is

one of {RZP, RNZP, RLZP, RNLZP} to check if the selected Rx is zero or negative.

Rx should not be provided for other conditionals. n is 1 or 2.