Clock Control

2-27MSP50C6xx Architecture

therefore, is 131.07 kHz, and the multiplier operates in increments of this base

frequency. The minimum multiplication of the base frequency is 1, and the

maximum multiplication is 256. The resulting master clock frequency, there-

fore, can be varied from a minimum of 131.07 kHz to a maximum of

33.554 MHz, in 131.07 kHz steps.

From the master clock to the CPU clock, there is a divide-by-two in frequency.

The CPU clock, therefore, can be set to run between 65.536 kHz and the maxi-

mum achievable (refer to the data sheet), in 65.536 kHz steps.

The maximum required CPU clock frequency for the C6xx is 8 MHz over the

entire V

DD

range. This rate applies to the speed of the core processor. Higher

CPU clock frequencies may be achieved, but these are not qualified over the

complete range of supply voltages in the guaranteed specification.

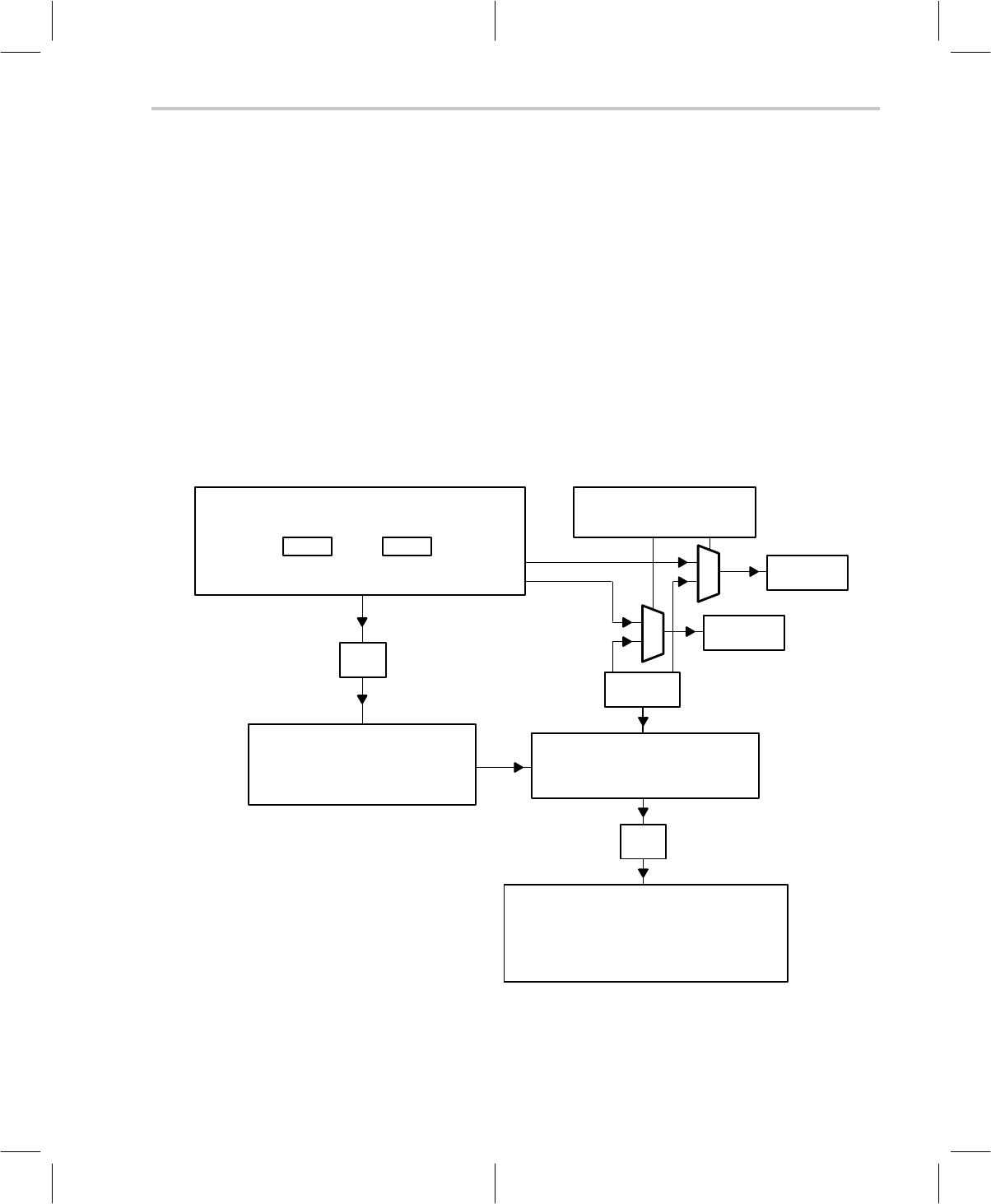

Figure 2–9. PLL Performance

Oscillator Reference

32 kHz

RTO CRO

Selection Made in ClkSpdCtrl

crystal

referenced

Resistor

Trimmed

or

PLL

Phase-Locked-Loop circuit

Multiplier Adjusted in ClkSpdCtrl

x 1 ... x 256

x4

Timer Source Option

Selected in IntGenCtrl

1

0

TIMER2

1

0

TIMER2

÷2

MC

Master Clock : Runs Periphery

131.07 kHz ... 33.554 MHz

÷2

CPU Clock

Core-Processor Speed

65.536 kHz ... F

MAX

(F

MAX

= 8 MHz)